[Xilinx]Modelsim独立仿真Vivado生成的PLL核

EDA Tools:

1、Vivado 2015.1(64-bit)

2、Modelsim SE-64 10.1c

Time:

2016.05.26

-----------------------------------------------------------------------------------

喜欢使用Modelsim工具独立进行代码的仿真。也不是Vivado自带的不好(至少目前的小代码没啥影响)

只是在一个vivado工程进行仿真时,添加文件的功能没用太明白,好烦!

--

大前提:和Altera一样,也是需要先将底层的模块编译为库。这个步骤其实是一劳永逸。编译一次,以后

仿真用到时,只需添加使用到的编译库的目录即可,节省时间成本。

当然,如若乐意,你也可自行添加底层模块的源码到Modelsim当前工程。

--

Vivado更为便捷的是直接提供GUI按钮来一键编译Modelsim仿真所需的库(当然,并非所有都编译)。

-----------------------------------------------------------------------------------

tb代码:

1 `timescale 1ns/1ns 2 3 module tb; 4 5 reg clk_in1 = 0; 6 reg reset = 1; 7 8 always #5 clk_in1 = !clk_in1; 9 10 initial begin 11 #10; 12 repeat(50) @(posedge clk_in1); 13 reset <= 0; 14 end 15 16 17 //全局复位 18 glbl glbl(); 19 20 pll_OSC_27M_system pll_OSC_27M_system_inst 21 ( 22 // Clock in ports 23 .clk_in1(clk_in1), // input clk_in1 24 // Clock out ports 25 .clk_out1(clk_out1), // output clk_out1 26 .clk_out2(clk_out2), // output clk_out2 27 .clk_out3(clk_out3), // output clk_out3 28 .clk_out4(clk_out4), // output clk_out4 29 // Status and control signals 30 .reset(reset), // input reset 31 .locked(locked)// output locked 32 ); 33 34 35 initial begin 36 #10; 37 repeat(200) @(posedge clk_in1); 38 $stop; 39 end 40 41 42 endmodule

试验过程:

1、最开始tb里面是没有第18行的。

然后,源码添加tb.v、pll_name.v和pll_name_clk_wiz.v这三个模块。

这时,会提示pll_name_clk_wiz模块里面例化到的一些底层模块找不到。

具体是:

Instantiation of 'PLLE2_ADV' failed.

Instantiation of 'BUFG' failed.

2、根据经验,这就是需要添加搜索库的路径。

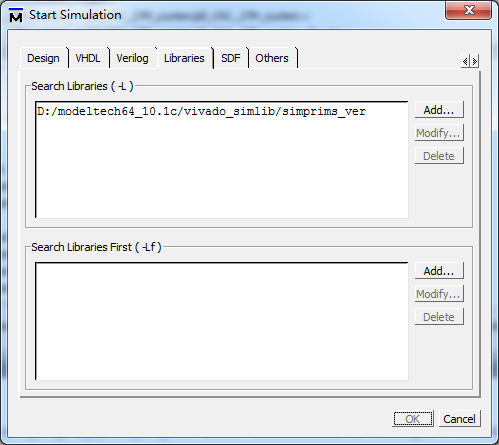

具体GUI操作就是:Simulate -->Start Simulation

默认是Design标签处于激活,先切换到Libraries标签,

在Search Libraries(-L)添加需要使用到的库(这里仅需要simprims_ver)的路径。

比如我的情况是:

接着,再切换到Design标签,展开work,选择tb(最顶层模块),然后选择ok。

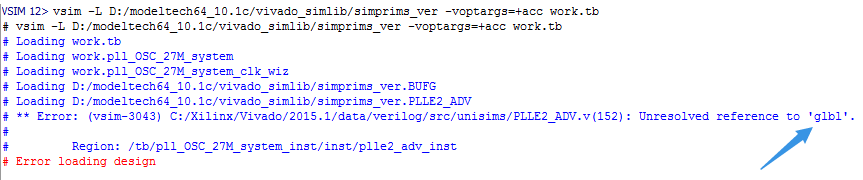

3、但发现还是有问题!截图如下:

网络搜索下,了解这是xilinx全局复位的模块。

该模块在C:\Xilinx\Vivado\2015.1\data\verilog\src

路径其实在上面Error提示的一部分。

4、于是,自己copy一份glbl.v到当前工程,进行编译。

但还是弹出相同的错误提示。

只好打开PLLE2_ADV.v模块的代码,搜索glbl关键字。

发现代码有2处用到glbl,具体分别是:

第152行:

tri0 GSR = glbl.GSR;

第1645行:

assign (weak1, strong0) glbl.PLL_LOCKG = (glock == 0) ? 0 : p_up;

----

注意到上面都是层次调用。

换言之,我们需要tb例化glbl,且例化名只能取glbl。

这便有了前面pose的tb代码的第18行!

-----------------------------------------------------------------------------------

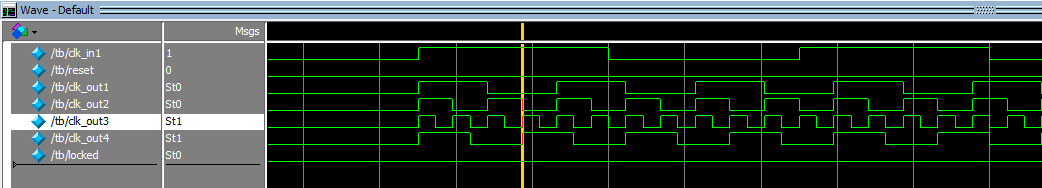

仿真波形:

这是全局视图。可见locked信号还是一样,高电平表示时钟锁住,呈稳定状态。

这是局部视图1。此时刚开始产生输出时钟波形,但locked尚未有效!

注意到PLL设置的同相对应的是各个输出时钟的上升沿。

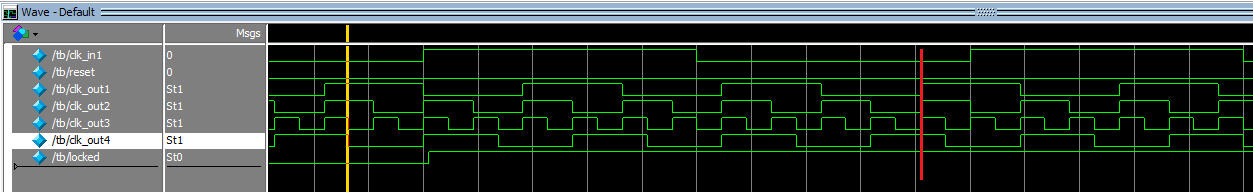

这是局部视图2。此时locked正要拉高。

----------------------------------

OVER!

浙公网安备 33010602011771号

浙公网安备 33010602011771号