彻底搞懂IIC总线(7)I2C总线硬件电气连接-上拉电阻-阻尼电阻-总线电容-I3C协议

本文由德力威尔王术平原创,转载、引用请注明出处,否则侵权。

摘要

本文详细介绍了I2C总线上拉电阻、串联电阻、漏电流的计算方法,给出了总线电容过大的解决方案,并指出了总线的布局布线方法,同时对MIPI-I3C进行了简要介绍。

七. I2C总线设备与总线线路的电气连接

7.1 上拉电阻的取值

本小节仅对标准模式、快速模式和快速增强模式的上拉电阻取值进行说明。高速模式虽说也有上拉电阻,但其主机内部集成了恒流源,可以加快tr,所以对上拉电阻不做特殊规定;超快速模式是推挽输出,单向传输,无需上拉电阻,而且使得tr更快;所以本I2C规范中没有对高速模式和超快速模式上拉电阻进行单独说明。

7.1.1上拉电阻的最大取值

7.1.1.1 用Rp(max)和Cb函数关系图求上拉电阻Rp(max)

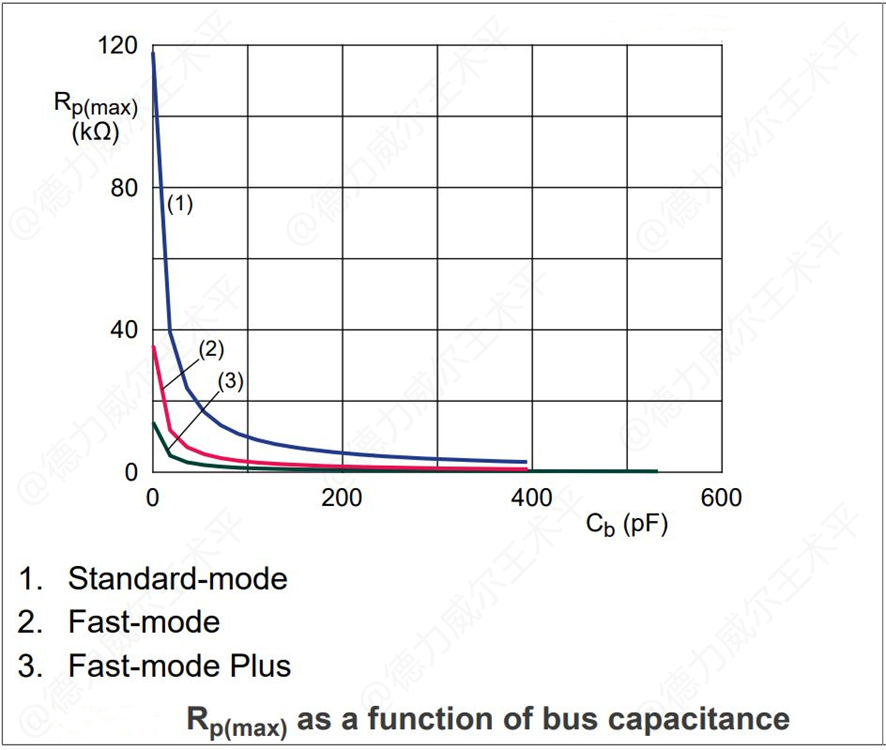

总线电容Cb是器件引脚、连接导线的总电容。在上升时间(tr)一定的情况下,此电容限制了上拉电阻Rp的最大值。图1-71给出了上拉电阻Rp(最大值)与总线电容的函数关系。我们就可以用这个图标估算出上拉电阻Rp(最大值)。

图1-71 上拉电阻Rp(max)与总线电容Cb的函数关系

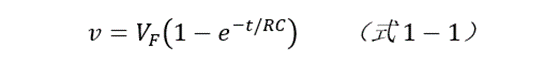

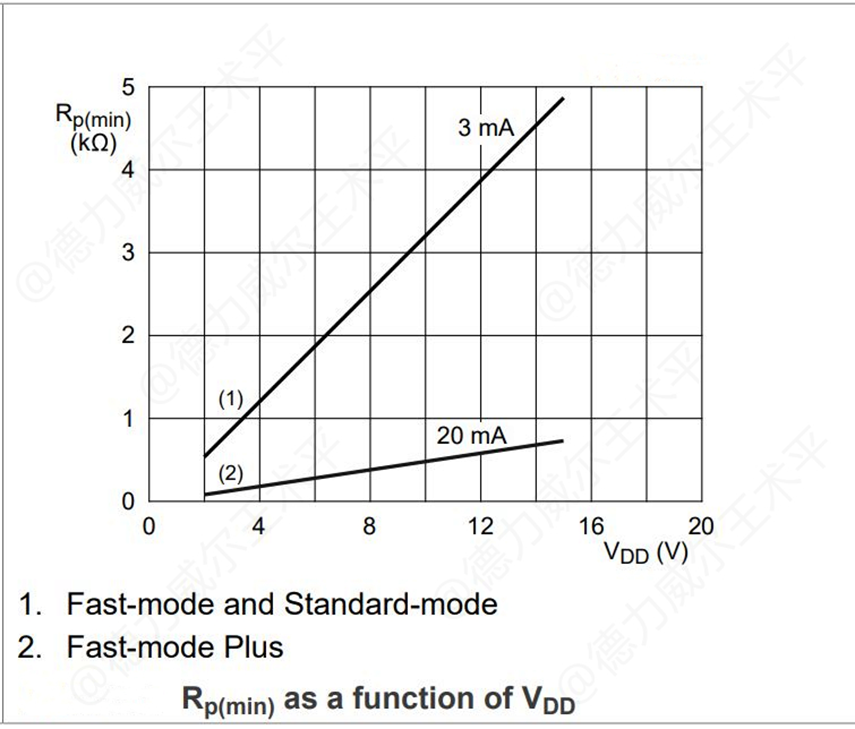

7.1.1.2 用电容充电公式求上拉电阻Rp(max)

下面我们计算一下上升时间(tr):

已知输入电平阈值与VDD相关:VIH = 0.7VDD,VIL = 0.3VDD。根据电容充电公式(见式1-1):

可以得到:v(t) = VDD (1 - e-t / RC),其中t是充电时间,RC是时间常数。

电容充到0.3VDD的时间:v(t1)= 0.3×VDD = VDD(1-e-t1/RC),那么t1 = 0.3566749×RC;

电容充到0.7VDD的时间:v(t2)= 0.7×VDD = VDD(1-e-t2/RC),那么t2 = 1.2039729×RC;

上升沿时间:tr = t2-t1 = 0.8473×RC。

可推出上拉电阻的公式(式1-2):

式中,Rp(max)是上拉电阻的最大取值,单位Ω;Cb是总线上的负载总电容,单位F,标准模式、快速模式和快速增强模对应的总线上电气特征给出了Cb的值;tr是电容电压从0.3VDD上升到0.7VDD的上升时间,单位s,在标准模式、快速模式和快速增强模对应的总线上电气特征给出了tr的值。

图1-71函数关系图 和式1-2函数公式是等效的,都表示标准模式、快速模式和快速增强模式最大上拉电阻Rp与总线电容Cb的函数关系。我们可以用以上两种方法求上拉电阻Rp的最大值。显然用函数关系图估算比较快捷。

7.1.2上拉电阻的最小取值

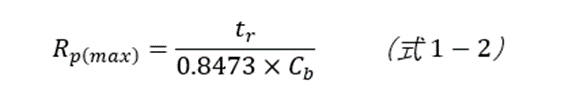

7.1.2.1 用Rp(min)和VDD函数关系图求上拉电阻Rp(min)

电源电压限制电阻Rp的最小值,因为标准模式和快速模式的额定最小吸电流为3 mA,快速增强模式为20 mA。Rp(min)作为VDD的函数,如所示Figure 42。

图1-72 上拉电阻Rp(min)与VDD的函数关系

图1-72 上拉电阻Rp(min)与VDD的函数关系

7.1.2.2 用欧姆定律关系求上拉电阻Rp(min)

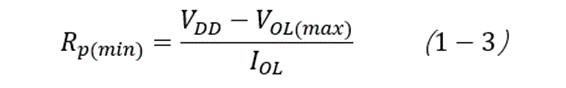

其计算公式如下(式1-3):

式中,Rp(min)为上拉电阻最小值,单位Ω;VDD电源电压,单位V;Vol(max)为输出低电平时的电压,单位V,在标准模式、快速模式和快速增强模式对应总线电气特征表中给出了值;Iol为输出低电平时的灌电流,单位A,在标准模式、快速模式和快速增强模式对应总线电气特征表中给出了值。

我们可以用上述两种方法求出上拉电阻Rp(min),显然用函数关系图来估算比较快捷。

7.2 解决总线电容Cb过大的方法

总线电容限值用于限制上升时间的减少,以满足在额定传输频率。虽然大多数设计可以轻松保持在这一限制范围内,但有些应用可能会超过这一限制。系统设计人员可以采用以下几种方法来应对过大的总线电容:

①降低fSCL频率(见12.2.1):总线以较低的速度运行(较低的fSCL)。

②增加输出驱动能力(见12.2.2):可以使用驱动电流更高的器件,如额定为快速模式增强的器件(PCA96xx)。

③使用总线缓冲器(见12.2.3):有许多总线缓冲器件可以将总线分成若干段,使每段的电容低于容许限值,例如PCA9517总线缓冲器或PCA9546A开关。

④增加开关上拉电路(见12.2.4):开关上拉电路可用于加速上升沿,方法是在需要时交替切换低值上拉电阻的输入和输出。

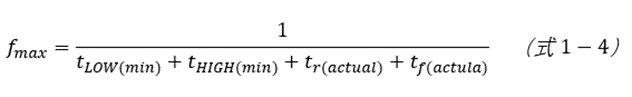

7.2.1 降低fSCL频率

要确定允许的较低总线工作频率,首先要找到总线上限制最大(运行速度最低)的器件的tLOW和tHIGH。有关这些值,请参考各个器件的数据表。实际上升时间(tr)取决于RC时间常数。最大限制下降时间(tf)取决于总线上的最低输出驱动。确保考虑到任何具有最小tr或tf的器件。上限频率计算公式为(式1-4):

式中,fmax为运行工作频率上限,单位是s;tLow(min)为SCL低电平保持最小时间,单位s;tHIGH(min)为SCL高电平保持最小时间,单位s;tr(actual)为SCL上升沿实际时间,单位s;tf(actual)为SCL下降沿实际时间,单位s。

备注:如果总线很长,还必须考虑信号的飞行时间。

实际结果可能更慢,因为实际运行时不会准确地将tLOW和tHIGH分别控制在30 %至70 %或70 %至30 %的最小值。

7.2.2 增强输出驱动能力

如果使用PCA96xx Fast-mode Plus或P82B总线缓冲器等更高驱动器件,则更高强度的输出驱动器会吸收更多电流,导致边沿速率显著加快,也就允许更高的总线电容。参考相关的总线上电气特征参数,使用Cb、Rp、tr和tf的实际值进行计算,以确定最大频率。

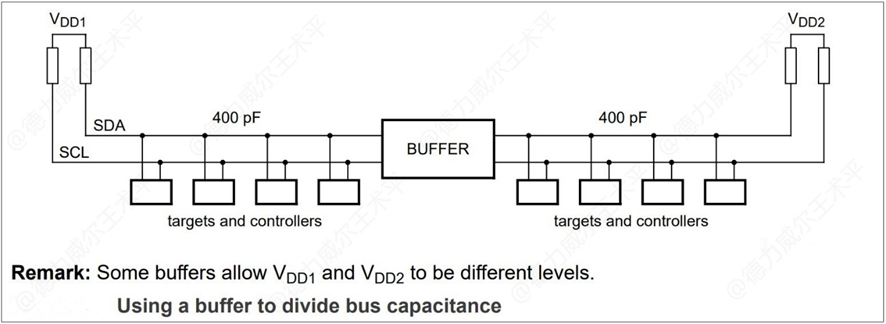

7.2.3 增加总线缓冲器、多路复用器和开关

另一种解决总线电容过大的方法是使用总线缓冲器、多路复用器或开关将总线分成更小的段。图1-73 显示了一个使用PCA9515缓冲器处理总线电容过大的示例。然后允许每个段具有最大电容,因此总线可以具有两倍的最大电容。请记住,添加缓冲总是会增加延迟——缓冲延迟,加上到每个边沿的额外转换时间,这降低了最大工作频率,并且还可能引入特殊的VIL和VOL考虑。

有关这方面的应用和恩智浦半导体器件的更多信息,请参考应用笔记AN 255(I2C / SMBus中继器、集线器和扩展器)和AN262(PCA 954 x系列I2C/SMBus多路复用器和开关)。

图1-73 使用缓冲器来驱动过大总线电容

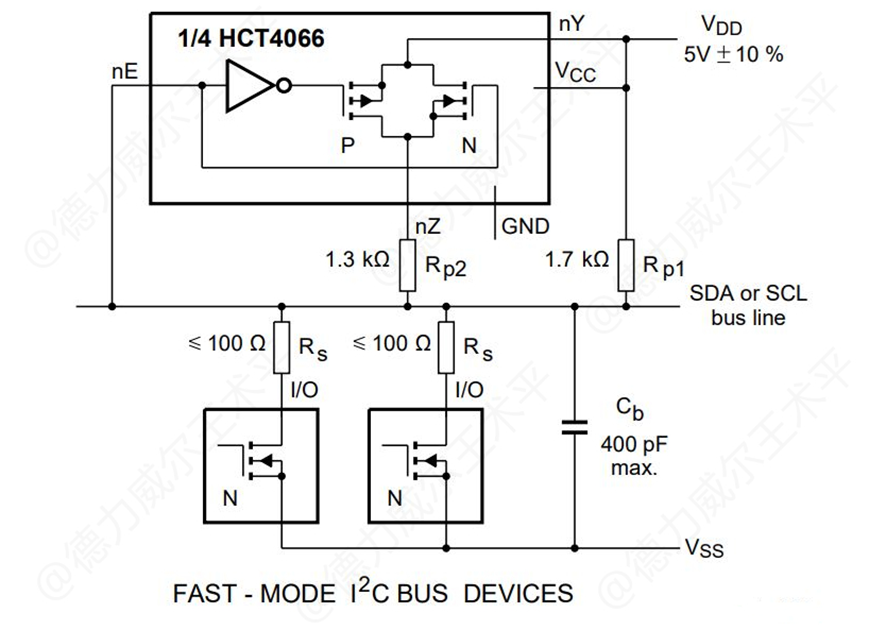

7.2.4 增加开关上拉电路

电源电压(VDD)和最大输出低电平决定上拉电阻Rp的最小值。例如,当电源电压为VDD = 5V±10%,VOL(max) = 0.4 V、电流为3 mA时,Rp(min)=(5.5-0.4)/0.003 = 1.7kΩ(参考式1-3)。如图1-71所示,Rp=1.7KΩ值将最大总线电容限制在200 pF左右,以满足300 ns的最大tr要求。如果总线电容高于此值,就可以使用如图1-74的开关上拉电路。

图1-74 增加开关上拉电路来驱动总线过电容

图1-74中的开关上拉电路适用于VDD = 5V±10%的电源电压和400 pF的最大容性负载。由于它是由总线电平控制的,因此不需要额外的开关控制信号。在上升/下降沿期间,HCT4066中的双向开关在0.8 V至2.0 V的总线电平下开启/关闭上拉电阻Rp2,组合电阻Rp1和Rp2可以在300 ns的最大额定上升时间(tr)内上拉总线。

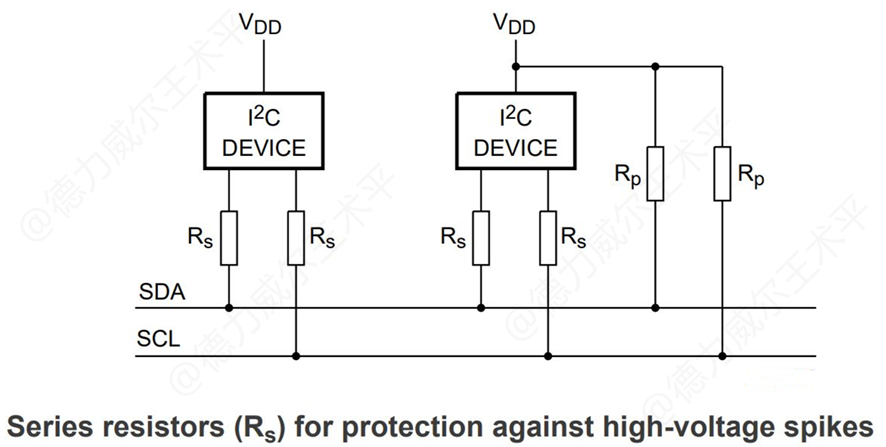

串联电阻rs是可选的。它们保护I2C总线设备的I/O级免受总线线路上高压尖峰的影响,并将总线线路信号的串扰和下冲降至最低。Rs的最大值由当总线切换到低电平以关闭Rp2时该电阻上的最大允许压降决定。

此外,有些总线缓冲器内部集成了上升时间加速器。也有一些独立的上升时间加速器器件可供选用。

7.3 串联保护电阻的取值

如图1-75例如,300Ω的串联电阻(Rs)可用于防止SDA和SCL线路上的高压尖峰(例如,由电视显像管的闪烁引起)。如果使用串联电阻,设计人员必须将Rs电阻加入Rp和容许总线电容Cb的计算中。

图1-75 I2C总线的串联保护电阻

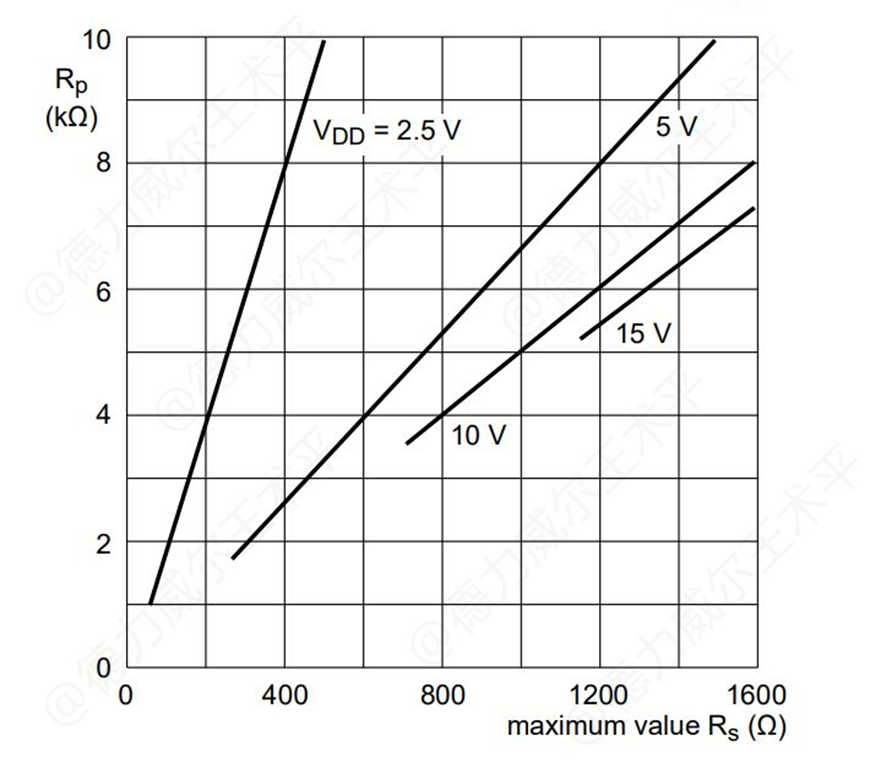

低电平所需的0.1VDD噪声裕量限制了Rs的最大值。Rs(max)与Rp的函数关系如图1-76所示。请注意,串联电阻会影响输出下降时间。

图1-76 串联电阻Rs与上拉电阻的函数关系

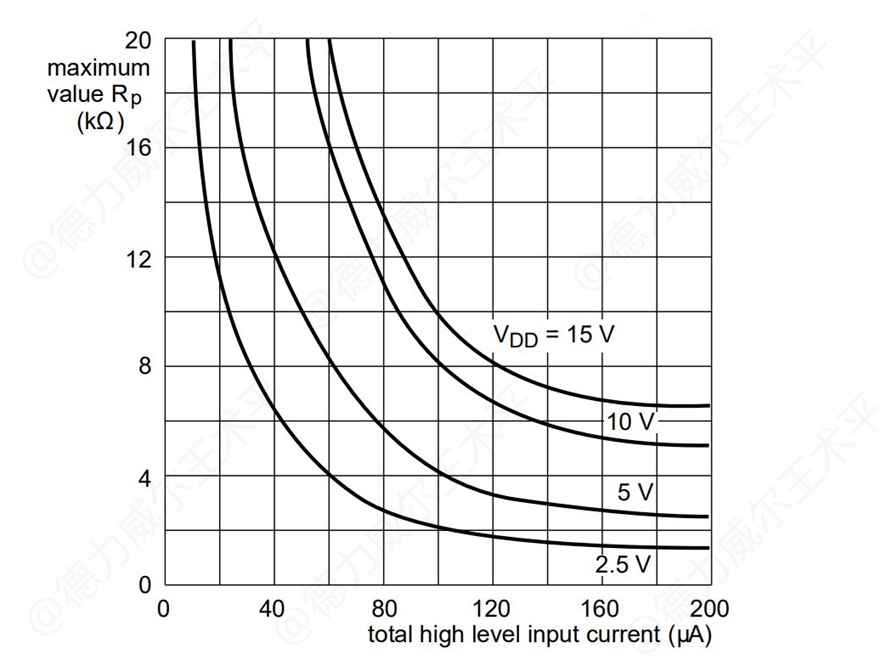

7.4 输入漏电流

每个连接到I2C的器件的最大高电平输入电流的额定最大值为10 μA,由于高电平要求0.2VDD的噪声裕量,该输入电流限制了Rp的最大值。这个限制取决于VDD。总的高电平输入电流与最大上拉电阻Rp(max)之间的函数关系如图1-77。

图1-77 高电平输入泄露电流与最大上拉电阻的函数关系

7.5 总线的走线方式

一般来说,必须优化I2C布线方式,以便将总线线路的串扰和干扰降至最低。由于上拉器件的阻抗相对较高,总线最容易受到高电平串扰和干扰的影响。

如果PCB或带状电缆上的总线长度超过10 cm,并且包括VDD和VSS线,则布线方式式应为:

如果没有VDD线,只有VSS线,走线方式应为:

这些布线方式还会导致SDA和SCL线路具有相同的容性负载。如果PCB板设计时有单独的VDD层和VSS参考层,则可以省略VSS和VDD线。

如果总线是双绞线,每条总线必须与VSS回路绞合。或者,SCL线可以与VSS回路绞合,SDA线与VDD回路绞合。在后一种情况下,必须使用电容将双绞线两端的VDD线与VSS线相连,以达到去耦的目的。

如果总线线路被屏蔽(屏蔽层连接到VSS),干扰将降至最低。但是,尽量使屏蔽电缆与SDA、屏蔽电缆和SCL线之间的分布等效电容最小,以最大限度地降低串扰。

八. 术语缩写

图1-78 术语缩写

九. MIPI I3C概述

9.1 I3C与I2C的关系

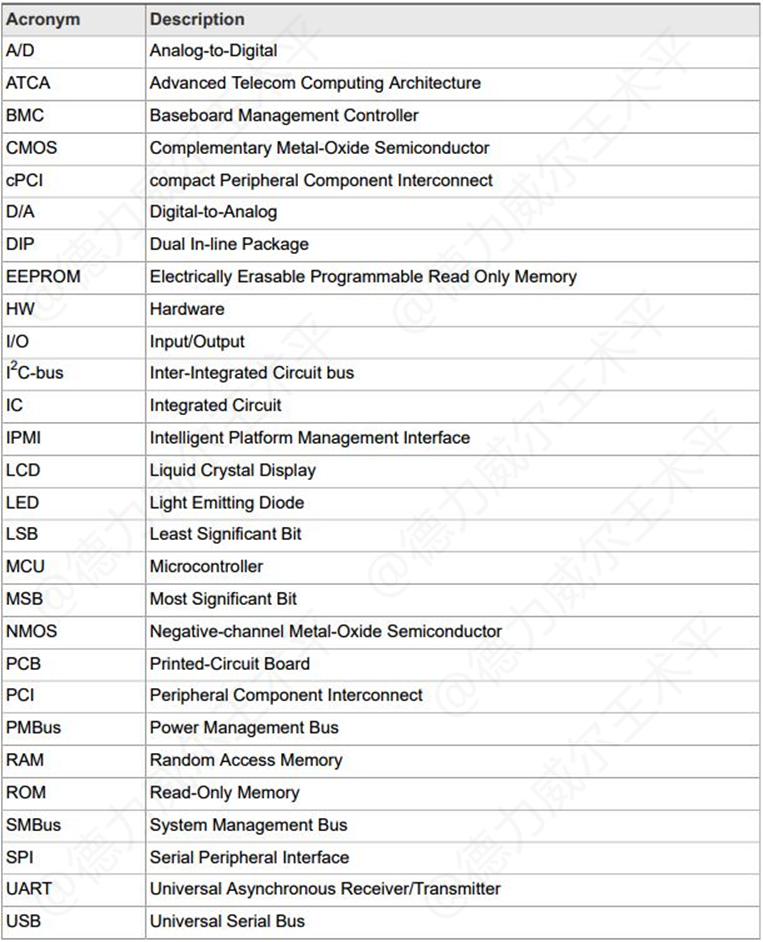

I3C是MIPI(Mobile Industry Processor Interface)移动产业处理器接口联盟推出的改进型I2C总线接口,全称是Improved Inter Integrated Circuit,因此简称为I3C。I3C仍然是采用2根通信线,一根数据线SDL,一根时钟线SCL。I3C向下兼容I2C,也就是I3C总线可以挂载传统I2C接口的器件,使用很是方便。MIPI联盟的新接口标准旨在通过减少传感器系统集成的物理引脚来实现传感器通讯的标准化,提供一个快速、低成本、低功耗、两线数字接口标准。

MIPI I3C(和公开上市的MIPI I3C Basic)提供了一种可扩展的中速实用控制总线,用于将外设连接到应用处理器。其设计融合了I2C总线和SPI接口的关键特性,提供统一的高性能、低功耗接口解决方案,为I2C总线和SPI实施者提供灵活的升级路径。I3C最初于2017年推出,是一个发展多年的项目,该项目基于与MEMS和传感器行业以及更广泛的电子生态系统的广泛合作。

如图1-79所示,I2C总线从机(带50 ns滤波器)可以与工作在12.5 MHz的I3C主机共存,使现有的I2C总线设计能够移植到I3C规范。相反,以典型的400 kHz或1 MHz I2C总线速度运行的I3C从机可以与现有的I2C总线主机共存。

图1-79 I2C与I3C目标设备混用系统

就像I2C一样,I3C是通过标准CMOS I/O引脚使用双线接口实现的,但与I2C不同,I3C它无需另外的中断线,从机设备使用软中断能够通知主机设备中断,这一设计功能消除了对每个从机设备的单独中断线连接的需要,从而降低了系统成本和复杂性。I3C支持动态地址分配有助于最大限度地减少引脚数量,这对于适应空间受限的外形至关重要。

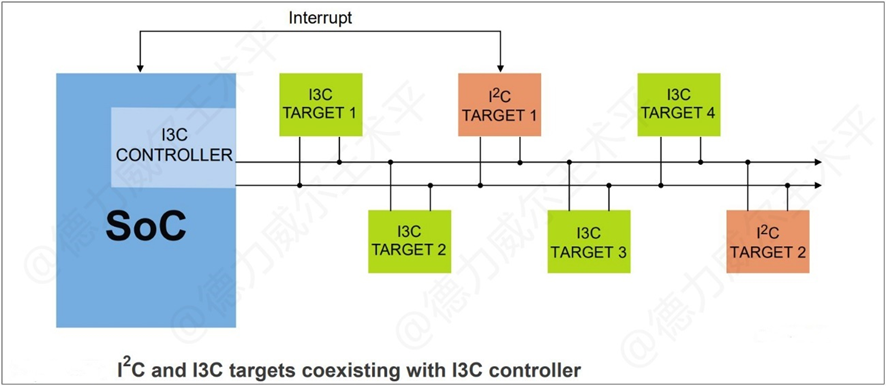

I3C支持多点总线,在12.5 MHz时,支持10 Mbps的标准数据速率(SDR),并提供高数据速率(HDR)模式选项。最终结果是,与I2C相比,I3C在性能和能效方面实现了飞跃,两者对比如图1-80所示。

图1-80 I3C和I2C能耗与速率对比

I3C的其他技术亮点包括多主机支持、动态寻址、命令代码兼容性以及睡眠模式等高级电源管理功能的统一方法。它提供同步和异步时间戳,以提高融合各种外设信号的应用的精度。它还可以快速批处理和传输数据,以最大限度地降低主机处理器的能耗。

9.2 I3C各版本功能比较

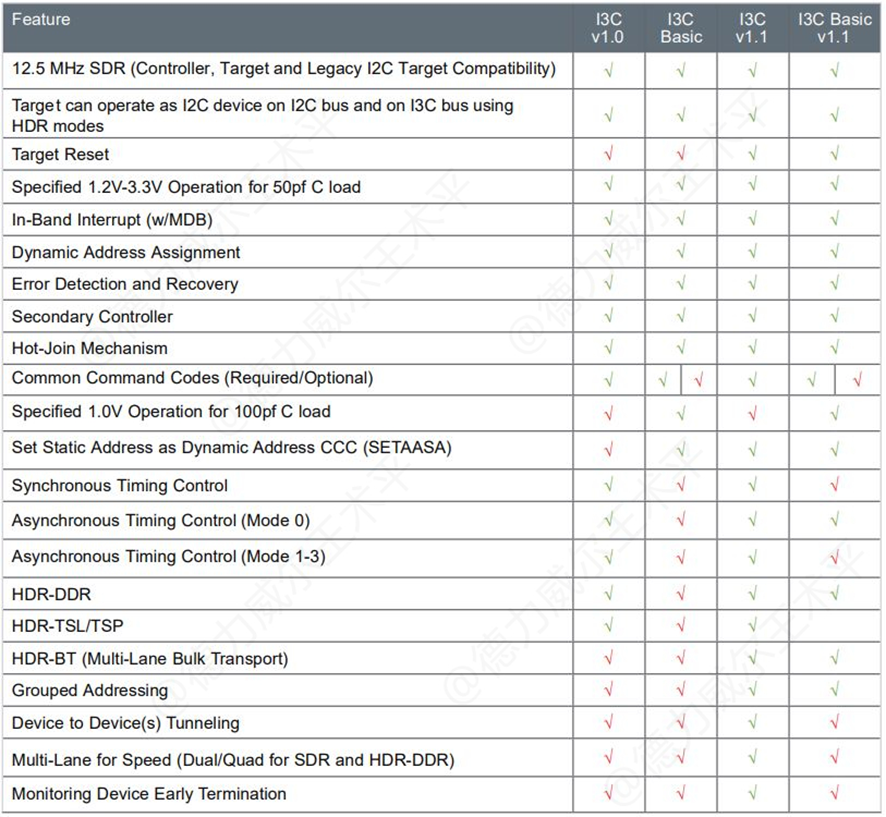

虽然I3C的完整版本仅面向MIPI联盟成员,但MIPI发布了一个名为I3C基础版的公共版本,其中捆绑了开发人员和其他标准组织最常用的I3C功能。I3C基础版无需MIPI会员即可实施,旨在为所有实施者提供一个免版税的许可环境。图1-81 总结了I3C和I3C基本版支持的主要功能。

图1-81 I3C各版本功能比较

为了支持开发人员,不同I3C实现之间的兼容性已经通过多个互操作性研讨会得到了确认,并且有几个支持MIPI的资源可用。其中包括:I3C主机控制器接口-MIPI I3C人机界面;用于Linux的I3C HCI驱动程序;I3C查找和配置规范—适用于I3C的DisCo;I3C调试和测试接口–I3C MIPI调试。

I3C知识产权(IP)可从多个供应商处获得,包括I3C基础版的免费许可版本。多家供应商也提供I3C一致性测试和验证IP测试套件。

有关I3C的更多信息,请访问MIPI联盟网站: https://www.mipi.org/specifications/i3c-sensor-specification。

本文由德力威尔王术平原创,转载、引用请注明出处,否则侵权。

本文参考资料:

①https://www.nxp.com/docs/en/user-guide/UM10204.pdf。

②https://www.nxp.com/docs/en/application-note/AN10216.pdf。