彻底搞懂IIC总线(6)I2C总线电气规范和传输时序

本文由德力威尔王术平原创,转载、引用请注明出处,否则侵权。

摘要

软硬件开发必备参考文档:本文详细的阐述了I2C 总线在标准模式、快速模式、快速增强模式、高速模式、超快速模式下的电气特征和传输时序。

六. I/O级和总线线路的电气规格和时序

6.1 标准、快速和快速增强模式设备

6.1.1 I/O口电气特征

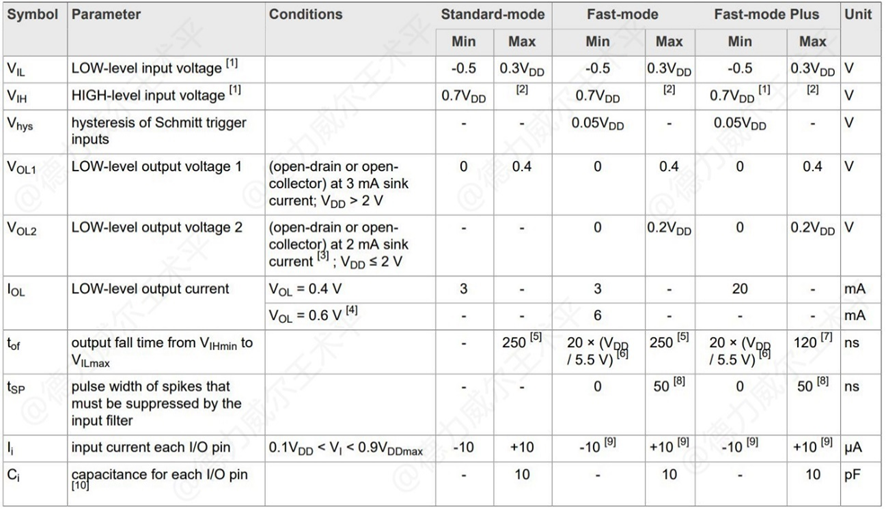

I/O电平、I/O电流、尖峰抑制、输出斜率控制和引脚电容如图1-62所示。I2C总线时序特性、总线电容和噪声容限也在图1-62中给出。

1-62 标准、快速和快速增强模式SDA、SCL的I/O口电气特征

备注:

[1] 一些传统标准模式器件的固定输入电平为VIL = 1.5 V,VIH = 3.0 V,请参考器件数据手册。

[2] 最大VIH = VDD(最大)+ 0.5 V或5.5 V,以较小者为准。参见元件数据表。

[3] 相同的RC时间常数, 3.0 V VDD供电,驱动电流为3 mA,而使用< 2 V VDD时消耗的电流更小。

[4] 为了在400 kHz下驱动全总线负载,0.6 V VOL下需要6 mA IOL,不符合此规格的器件仍可工作,但在400 kHz和400 pF下则不行。

[5] 实际SDA和SCL总线的tof最大为300 ns,本表规定tof额定最大为250 ns,这是为在SDA/SCL引脚之间串联保护电阻(rs )留的余量。

[6] 必须向后兼容快速模式。

[7] 在快速增强模式中,输出级和总线时序的下降时间相同。如果使用串联电阻,设计人员在考虑总线时序时应考虑到这一点。

[8] SDA和SCL输入上的输入滤波器抑制小于50 ns的噪声尖峰。

[9] 如果VDD关闭,快速模式和快速模式增强器件的I/O引脚不得阻碍SDA和SCL线。

[10] 多路复用器和开关等专用器件可能会超过此电容,因为它们将多条路径连接在一起。

6.1.2 总线上电气特征

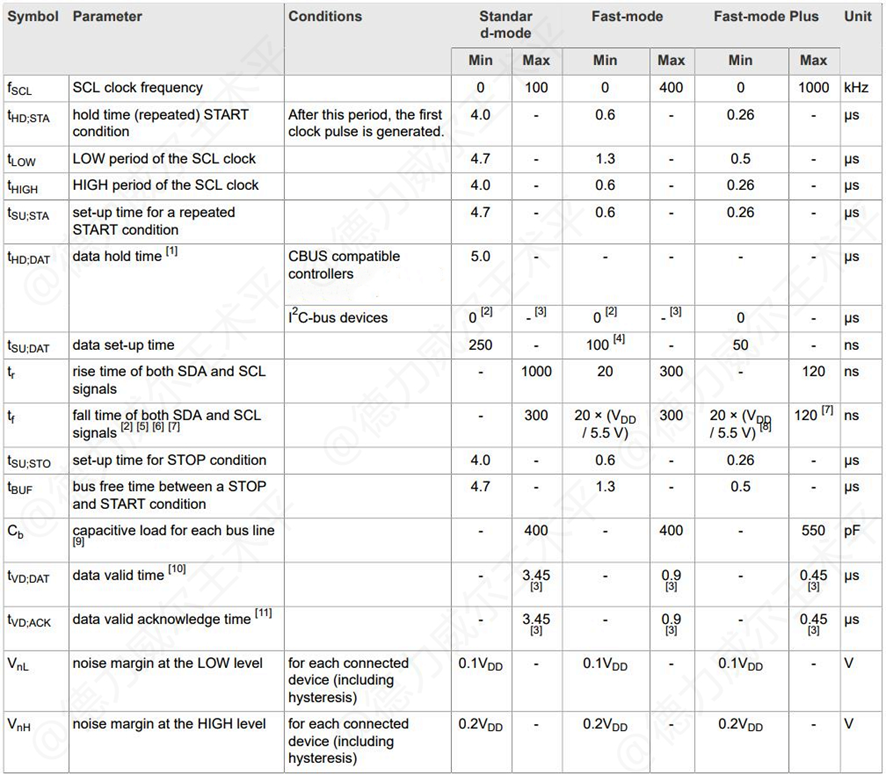

标准、快速和快速增强模式I2C总线设备的SDA和SCL总线特性,在图1-63给出。图中的电平值均参考图1-62中的相关参数。

图1-63 标准、快速和快速增强模式SCL、SDA总线上电气特征

备注:

[1] tHD;DAT是从SCL下降沿开始测量的数据保持时间,适用于传输和应答中的数据。

[2] 确保在SDA进入0.3VDD至0.7 VDD的不确定范围之前,SCL在下降沿降至0.3 VDD以下。

[3] 最大tHD;DAT对于标准模式和快速模式,可以是3.45 μs和0.9 μs,但必须小于tVD的最大值;tHDDAT或tVD通过转换时间确认。只有当器件不延长SCL信号的低电平周期(tLOW)时,才能满足该最大值。如果时钟延长了SCL,在释放时钟之前,数据必须在建立时间之前有效。

[4] 快速模式的I2C总线设备可以用在标准模式的I2C总线系统中,但是要求tSU;DAT必须满足250 ns。如果该设备不延长SCL信号的低电平周期,这将自动成为这种情况。如果这种器件延长了SCL信号的低电平周期,它必须将下一个数据位输出到SDA线tr(max)+Tsu;DAT=1000 + 250 = 1250 ns(根据标准模式I2C总线规范)。此外,应答时序必须符合该建立时间。

[5] 如果与高速模式器件混合,最快的下降沿时间参考图1-62参数。

[6] SDA和SCL总线的最大tf指定为300 ns。SDA输出级tf的最大下降时间规定为250 ns。这允许在SDA和SCL引脚与SDA/SCL总线之间连接串联保护电阻,而不会超过最大额定tf。

[7] 在快速模式Plus中,输出级和总线时序的下降时间相同。如果使用串联电阻,设计人员在考虑总线时序时应考虑到这一点。

[8] 必须向后兼容快速模式。

[9] 根据应用的实际工作电压和频率,允许的最大总线电容可能不同于该值。后面章节讨论应对较高总线电容的技术。

6.1.3 总线时序定义

图1-64 显示了I2C总线的时序定义。

图1-64 标准、快速和快速增强模式I2C总线时序

6.2 高速模式设备

6.2.1 I/O口电气特征

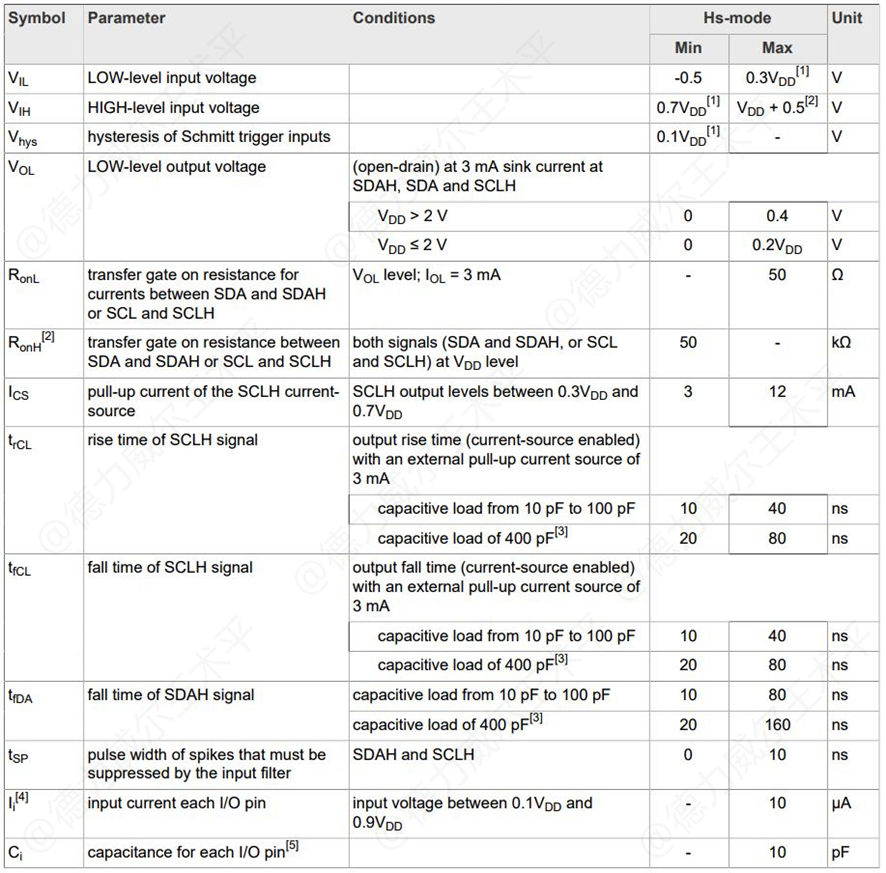

I2C总线高速模式器件的I/O电平、I/O电流、尖峰抑制、输出斜率控制和引脚电容在图1-65中给出。总线线路上高电平和低电平的噪声容限与F/S模式I2C总线设备的规定相同。

图1-65 高速模式I/O口电气特征

备注:

[1] 使用不符合预期I2C总线系统电平的非标准电源电压的设备必须将其输入电平与上拉电阻Rp所连接的VDD电压相关联。

[2] 提供SDA与SDAH、SCL与SCLH互转的电平转换的器件必须能够承受5.5 V的最大输入电压。

[3] 对于100 pF至400 pF的容性总线负载,上升和下降时间值必须进行线性插值。

[4] 如果其电源电压已经关闭,高速模式目标设备的SDAH和SCLH I/O级必须具有悬浮输出。由于电流源输出电路通常有一个VDD箝位二极管,因此这一要求对于Hs模式主机器件的SCLH或SDAH I/O级不是强制性的。这意味着Hs模式主机设备的电源电压无法在不影响SDAH和SCLH线的情况下关闭。

[5] 多路复用器和开关等专用器件可能会超过此电容,因为它们将多条路径连接在一起。

6.2.2 总线上电气特征

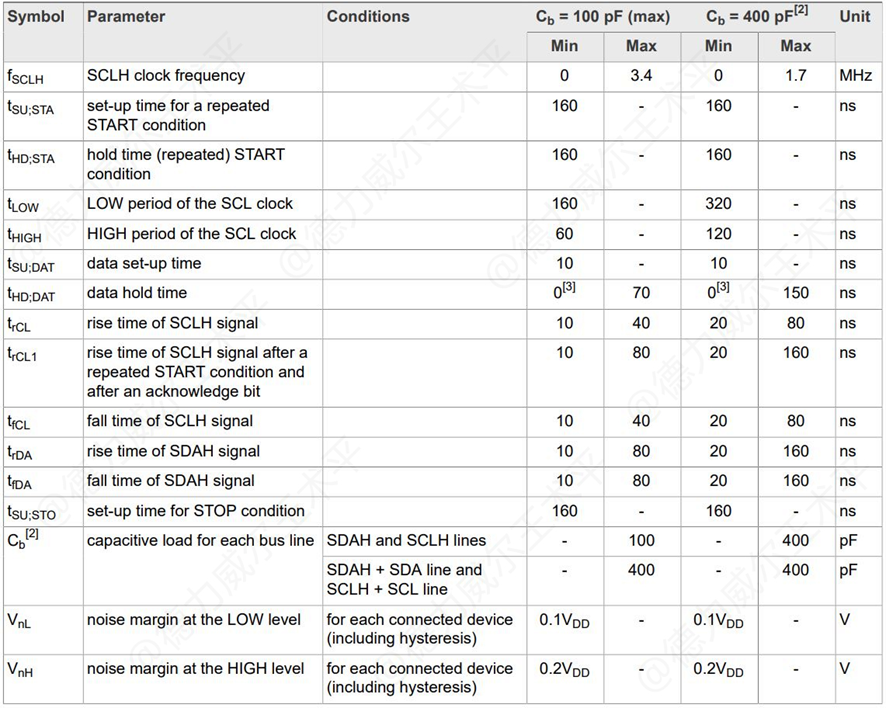

图1-66 显示高速模式总线上电气特征[1]。

图1-66 高速模式I2C总线电气特征

备注:

[1] 所有数值均参考VIH(最小)和VIL(最大)水平(参见图1-65)。

[2] 对于100 pF和400 pF之间的总线负载Cb,时序参数必须进行线性插值。

[3] 设备必须在内部提供数据保持时间,以桥接SCLH信号下降沿的VIH和VIL之间的未定义部分。对于SCLH信号的下降沿,阈值尽可能低的输入电路可以最大限度地缩短保持时间。

6.2.3 总线时序定义

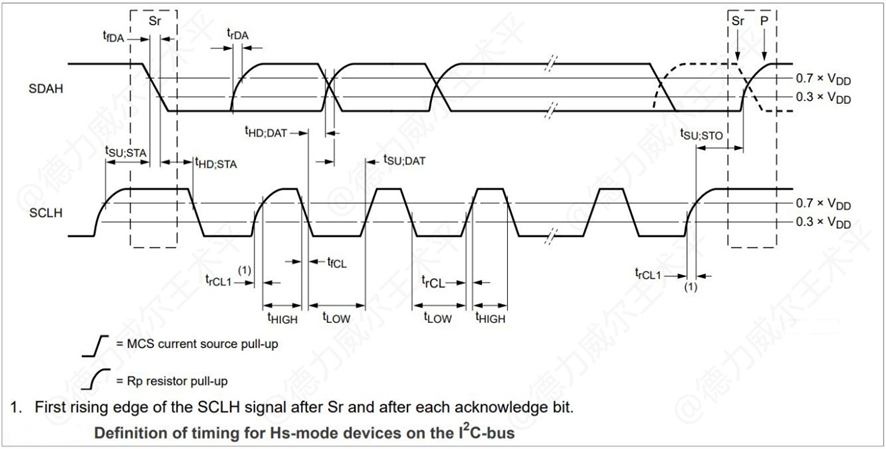

图1-67 是高速模式I2C总线时序定义:

图1-67 高速模式I2C总线时序定义

6.3 超快速模式器件

6.3.1 I/O口电气特征

I/O电平、I/O电流、尖峰抑制、输出斜率控制和引脚电容如图1-68所示。

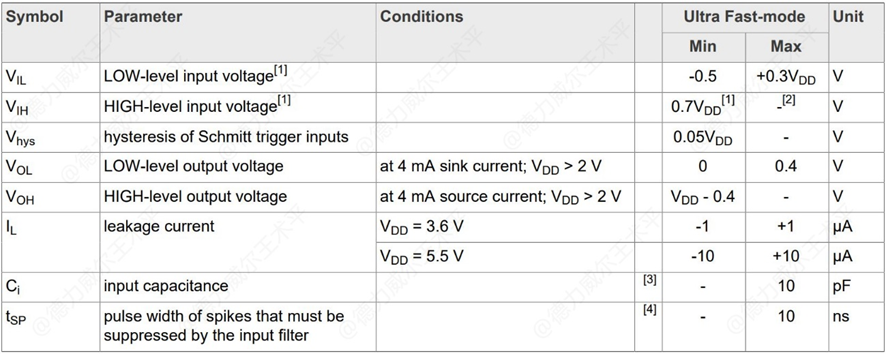

图1-68 超快速模式I/O口电气特征

备注:

[1] 有关实际电平阈值,请参考器件数据手册。

[2] 最大VIH = VDD(最大)+ 0.5 V或5.5 V,以较低者为准。参见元件数据表。

[3] 多路复用器和开关等专用器件可能会超过此电容,因为它们将多条路径连接在一起。

[4] USDA和USCL从机上的输入滤波器抑制小于10 ns的噪声尖峰。

6.3.2 总线上电气特征

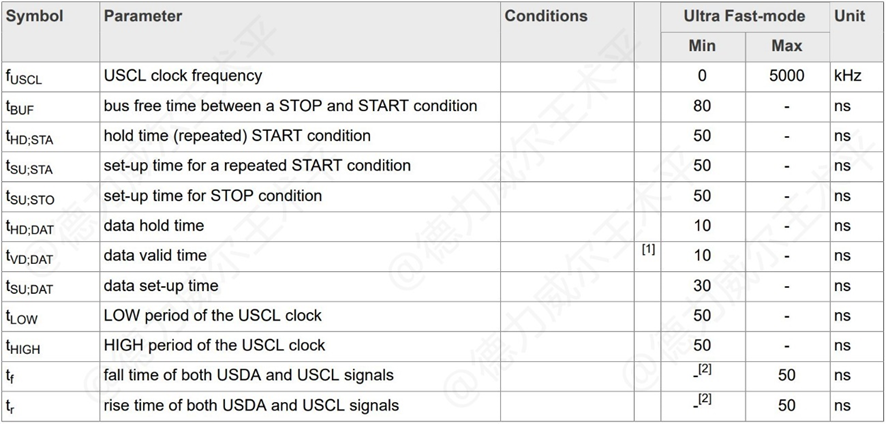

图1-69 显示超快速模式总线上电气特征。

图1-69超快速模式I2C总线上电气特征。

备注:

[1] tVD;DAT :在USCL变为低电平时,USDA输出电平有效的最小时间

[2] 从30 %VDD到70 %VDD(上升时间)或从70 %VDD到30 %VDD(下降时间),UFm信号的典型上升时间或下降时间为25 ns。

6.3.3 总线时序定义

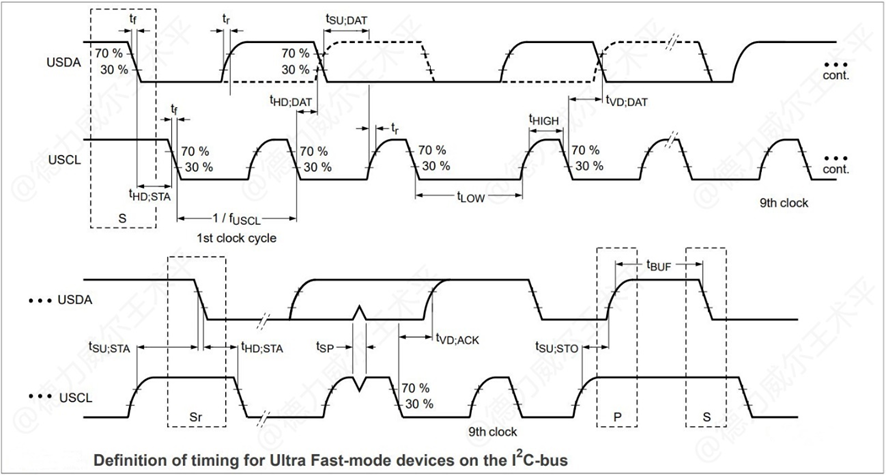

图1-70是超快速模式总线时序定义:

图1-70 超快速模式I2C总线时序定义

未完待续,请继续关注《彻底搞懂IIC总线(7)I2C总线电气连接》。

本文由德力威尔王术平原创;转载、引用请注明出处,否则侵权。

本文参考资料:

①https://www.nxp.com/docs/en/user-guide/UM10204.pdf。

②https://www.nxp.com/docs/en/application-note/AN10216.pdf。

浙公网安备 33010602011771号

浙公网安备 33010602011771号