1.1 Coherency Overview

系统component 可以不在软件的参与下维护共享memory 的cache 一致性,所有component 可以观测到memory 同一片区域的写操作。

ACE 现在有四个种类:ACE5、ACE5-Lite、ACE5-LiteDVM、ACE5-LiteACP;

Low-Power 参考AMBA Low Power Interface Specification。

1.2 Protocol Overview

ACE 协议基于AXI4提供的硬件一致性cache,ACE协议:

Cache 模型的五个状态,cache line 的状态决定下一步如何操作;

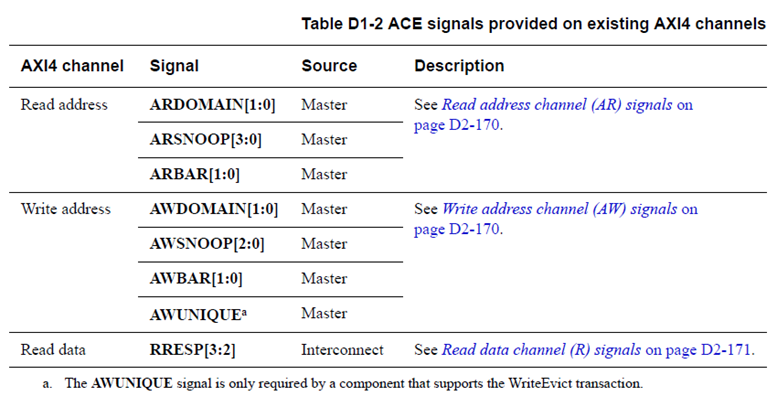

基于AXI4 通道基础上增加一致性信号;

Master 访问shared 地址通过额外的通道;

系统中保序传输所需要的Barrier 传输,ACE5、ACE5-Lite 不支持;

Distributed Virtual Memory 功能管理虚拟memory;

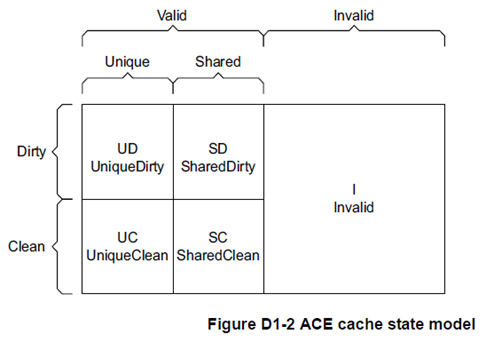

Valid、Invalid:指示当前cache line 是否有效;

Unique、Shared:指示当前cache line 是否在多个cache;

Clean、Dirty:指示当前cache line 数据是否跟main memory 数据一致;

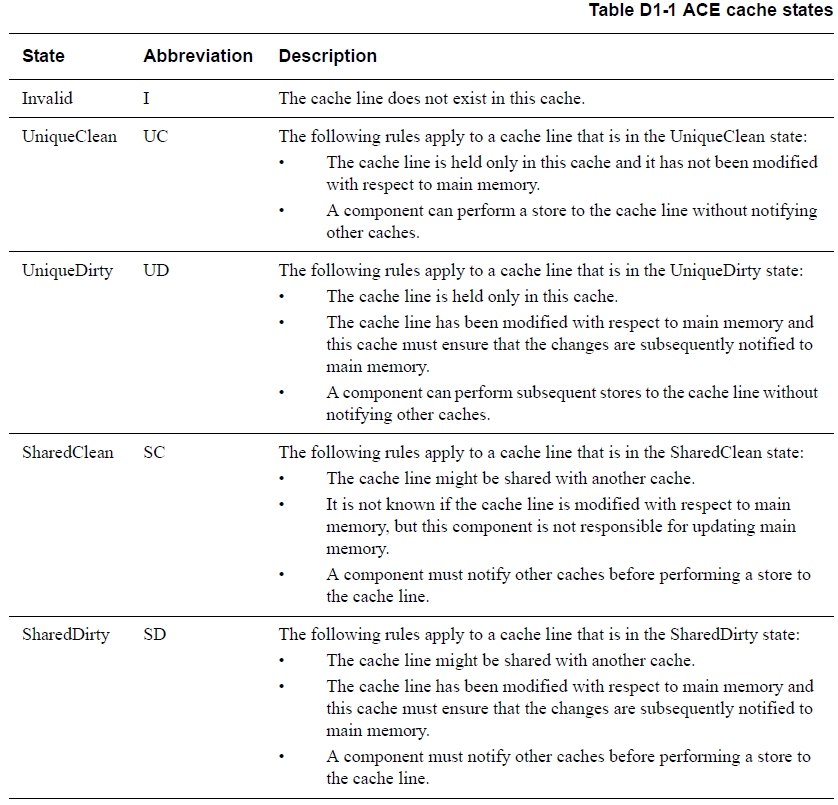

ACE cache line状态:

Cache 状态规则:

Unique状态必须只在一个cache;

多余一个cache 的line 必须为shared;

Cache 观测到line 有新的copy,必须copy 到本地;

Cache 丢弃自己的line,不同通知到其他cache,意味着有些shared cache line 其实只有一个copy 数据;

Line 数据更新,跟main memory 数据不一致,必须为Dirty;

Line 数据跟新,跟main memory 不一致,且有多个copy 在cache,必须只有一个cache 为Dirty;

1.3 Channel Overview

基于AXI4 新增通道:Snoop address channel (AC)、Snoop data channel (CD)、Snoop response channel (CR)。

AC:传输snoop 输入到cached master的控制信息;

CR:cached master 输出snoop 传输的response,每个snoop 传输只有一个response,包含CD 的data;

CD:cached master 输出copy data;

两个额外的acknowledge 信号,只是当前master 完成一次写、读传输。

1.3.1 应用举例

1.3.1.1 从Shared location load数据

- Maste 从AR 发起读操作;

- Interconnect 检查shareable 地址是否有copy,由snooped master component 发起;

- Snoop response 从snoop data 通道返回数据;

- 如果其他master cache已经有了数据,Interconnect 可以通过读数据通道返回initial master 数据;

- 如果没有snooped master 提供数据,则:

a) Interconnect 向main memory 发命令,跟initial master 发起操作一样;

b) 读数据通道返回数据给master; - Master component 使用RACK指示当前传输已经完成;

1.3.1.2 向shareable 地址store 数据

1.3.1.3 向部分cache line store 数据

1.3.1.4 向整个cache line store数据

1.3.1.5 Store 到cached

1.3.1.6 Overlapping store

1.4 Transaction overview

1.4.1 Non-snooping 传输

用于访问memory 空间,不在任何master cache 内,不会引起snoop 传输,主要用于:Non-shareable、Device;

No-shareable:ReadNoSnoop、WriteNoSnoop;

1.4.2 Coherent 传输

Shareable 区间的load操作,因为这些区间被其他component 的cache 保存。

从shareable区间Load :

向shareable 区间store:

访问shareable 区间但是不cache:

1.4.3 Memory update 传输

1.4.4 Cache 维护

Mater component采用广播的方式维护跟系统其他master 的cache。

1.4.5 Snoop 传输

Coherent 传输的一部分;

1.5 Transaction processing

Master component完成一次一致性传输处理流程:

- Initial master component 发起传输;

- 支持一致性要求:

a) 地址直达slave component;

b) Interconnect 支持一致性; - 一致性传输需要保序;

- Interconnect 检查snoop;

- 每个cached master 接受到snoop 传输后,必须返回response,有些还需要返回snoop data;

- Interconnect 检查是否需要访问main memory;

- Interconnect 收集snoop response和data;

- Initial master component 完成传输;

1.6 Concepts required for ACE specification

1.6.1 Domain

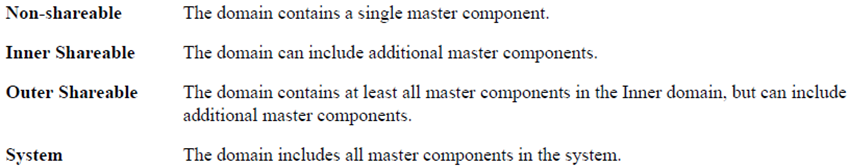

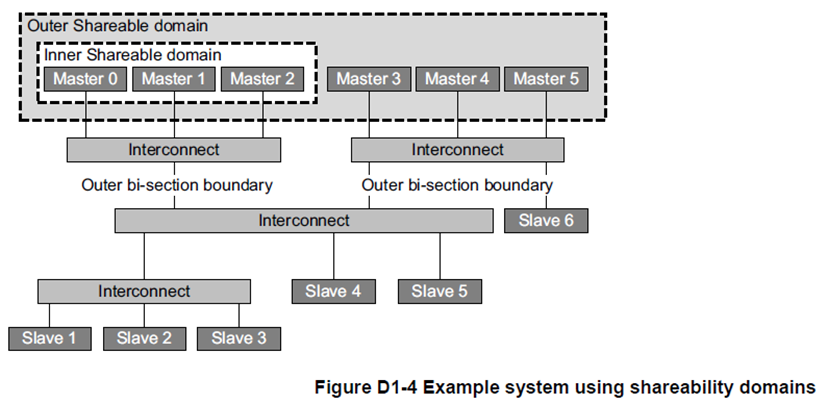

ACE协议使用shareability domain的概念,一个共享域为master component 为了一致性和barrier 传输的范围;

一致性中,master component使用检查共享域中其他master local cache 的一致性。Interconnect 检查是否需要通过snoop 。

Barrier 传输,master component使用共享域内是否有其他master 中是否有顺序依赖。

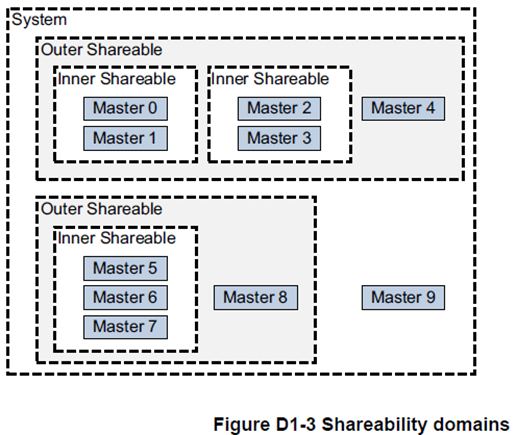

ACE总共有以下一些shareability domain:

Domain 划分原则:

Non shareable、Inner shareable、Outer shareable,每个master component 在每个域只能出现一次;

Domain 定义不能重叠;

使用System domain 的时候,每次传输都要被system 的其他master所检测;

举例:

对于图中Master0:

Master 0的cache line 为local cache;

Master 1-5的cache line 为peer cache;

Master 0-2的cache line 为Inner shareable domain;

Master 0-5的cache line 为Outer shareable domain;

Cache 0 为downstream cache;

1.6.2 Barriers

两种类型:

Memory barriers:master 发起barrier后的传输,都可以被domain 中的其他master 可观测;

Synchronization barriers:barrier 完成之前,要完成前面所有的传输;

Barrier 传输有地址和响应,没有数据,读写之间的barrier master 自己保证。

Master 自己保证发送命令的顺序,但是无法保证返回命令顺序,Barrier 是保证master 发出去的命令保序;

1.6.3 DVM

下图为典型virtual memory 系统:

Master 使用virtual address(VA) 访问;

SMMU 将VA转换为PA,TLB的cache 保存转换结果,TLB实现table walk转换;

SMMU 使用PA访问;

1.7 Protocol errors

两种错误类型:

Software protocol error:软件协议引起,多源头访问的位置shareable、cache 属性不匹配。会导致数据一致性错误,不会deadlock。只会出现在一个4KB区域,不会覆盖其他4KB区域。常用barrier 规避。如果读改写的操作使用AxCACHE[1]=1 访问,则不能保证。

Hardware protocol error:硬件发出不支持的操作,导致系统crash、lock up,或者其他non-recoverable 错误。

浙公网安备 33010602011771号

浙公网安备 33010602011771号