case中加与不加default的区别分析

上次有人问我在case中加与不加default的区别,我就说是不加default可能会生成latch,但对具体原因还是不太了解。后来一学长说在时序电路与逻辑电路中还有区别,这我更蒙了。

为了验证其内在原理我在quartus中进行建模,并且通过technology map viewer观察其schematic,实验过程如下:

一组合逻辑:

带default:

module case_combination(active,temp); input [3:0]active; output reg [2:0]temp; always @(active) begin case(active) 4'b1000:temp=3'b010; 4'b0100:temp=3'b011; 4'b0010:temp=3'b101; 4'b0001:temp=3'b000; default:temp=3'bxxx; endcase end endmodule

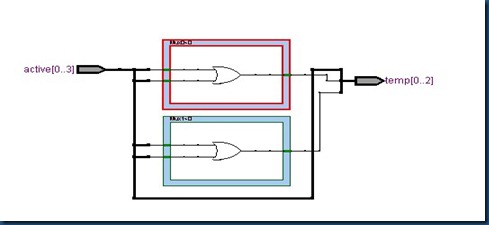

schematic1:

可以发现这个原理图比较简单,就两个or门.

module case_combination(active,temp); input [3:0]active; output reg [2:0]temp; always @(active) begin case(active) 4'b1000:temp=3'b010; 4'b0100:temp=3'b011; 4'b0010:temp=3'b101; 4'b0001:temp=3'b000; //default:temp=3'bxxx; endcase end endmodule

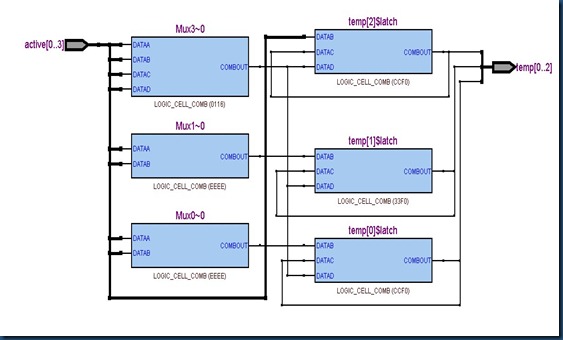

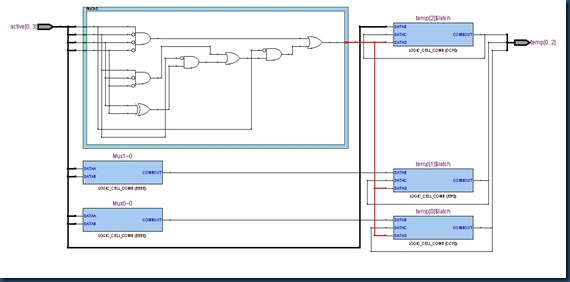

schematic2:

可以发现原理图明显变复杂,并且生成了三个latch,接着点开其中的模块有如下结构:

schematic3:

在schematic3中除了比schematic1中多了后三个latch外,前面部分由两个or门相同,但同时生成了一个比较复杂的逻辑电路,这个电路有什么用呢?请看schematic4:

schematic4:

可以看到那个逻辑电路的输出分别给了三个latch,原来这个逻辑电路就是用来产生latch的电平控制信号.当active的输入未在case的预定义中,那么将由这个逻辑电路控制latch的电平端为低电平,temp保持原有值.

二时序逻辑:

带default:

module case_timing(active,temp,clk); input clk; input [3:0]active; output reg [2:0]temp; always @(posedge clk) begin case(active) 4'b1000:temp<=3'b010; 4'b0100:temp<=3'b011; 4'b0010:temp<=3'b101; 4'b0001:temp<=3'b000; default:temp<=3'bxxx; endcase end endmodule

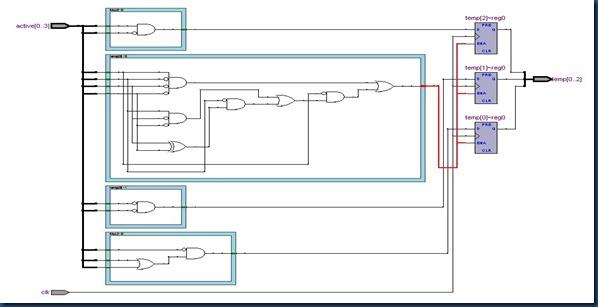

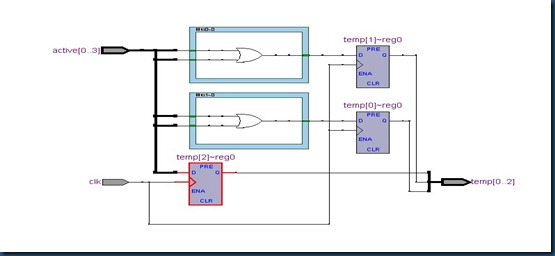

schematic5:

和schematic1相比就多了三个FF.

不带default:

module case_timing(active,temp,clk); input clk; input [3:0]active; output reg [2:0]temp; always @(posedge clk) begin case(active) 4'b1000:temp<=3'b010; 4'b0100:temp<=3'b011; 4'b0010:temp<=3'b101; 4'b0001:temp<=3'b000; //default:temp<=3'bxxx; endcase end endmodule

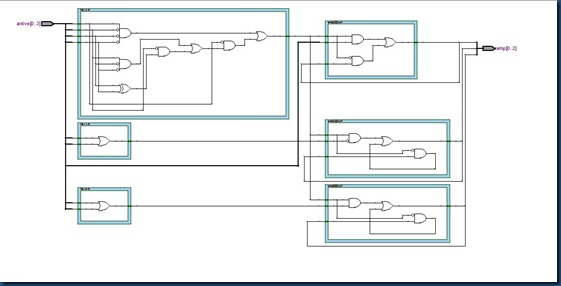

schematic6:

可以发现schematic6中并没有生成latch,依旧是那三个FF.问题的关键就在于FF中的ENA引脚.

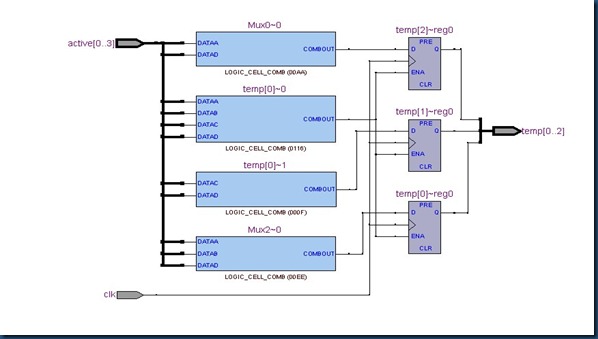

schematic7:

在schematic7中容易发现这个ENA引脚的输入就是与schematic4中相同的逻辑结构的输出,通过输出为低电平使FF的输入信号无效,从而保持FF原先的数据.

在schematic7中容易发现这个ENA引脚的输入就是与schematic4中相同的逻辑结构的输出,通过输出为低电平使FF的输入信号无效,从而保持FF原先的数据.

从这几个schematic的对比中我们可以有如下总结:

1,在组合逻辑中,不加default易生成latch,同时生成一个逻辑控制结构,浪费系统资源.

2,在时序逻辑中,不加default不会生成latch,但已经会生成一个逻辑控制结构,浪费系统资源.

总而言之,在写case语句中尽量加上default,以免浪费系统资源.

浙公网安备 33010602011771号

浙公网安备 33010602011771号