IO 口扩展

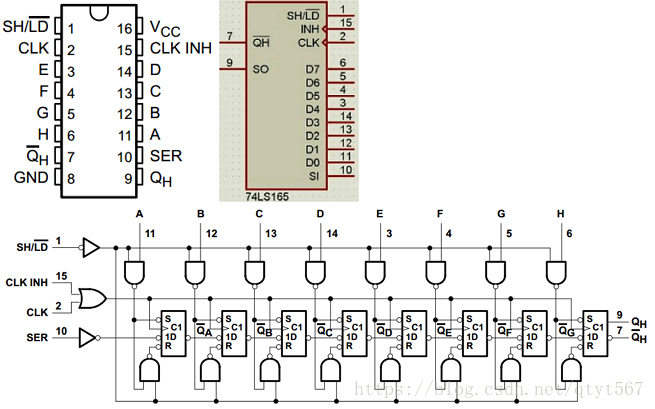

74LS165:8位并入、串出移位寄存器

①、SH/LD:移位与置位控制端;SH/LD置0,并行口的8位数据将被置入其内部的8个触发器,在SH/LD为1时,并行输入被封锁,移位操作开始;

②、INH:低电平时充许时钟输入,高电平时禁止时钟输入;

③、CLK:时钟输入,上升沿有效;

①、D0~D7:并行输入端。

⑤、SI:串行输入,用于扩展多个74LS165 的首尾连接端;

⑥、SO(QH):串行输出;

QH(反):也是串行输出端,它与 SO(QH)是反相的关系;

注意:

我刚开始总是读错一位,注意在SH/LD为低电平的锁存后,再变为高电平的时候,8个输入口的最高位已经在QH了,就是说第一位的数据是不需要时钟上升沿的,

/**

***************************************************************************************

* 函 数:74LS165读32位扩展引脚函数

* 参 数:无

* 返回值:state:读取的32位数据

***************************************************************************************

*/

unsigned long LS165_Read(void) //74LS165读32位扩展引脚函数

{

unsigned char i; //计数变量

unsigned long state = 0; //读取的32位数据

LS165_SH_LD = 0; //并行口的8位数据被置入内部的8个触发器

LS165_SH_LD = 1; //并行输入被封锁,移位操作开始

for(i=0;i<32;i++)

{

state = state<<1; //数据左移1位

if(LS165_DATA) //若引脚为高电平

{

state |= 0x01; //最低位置1

}

LS165_CLK = 0;

LS165_CLK = 1; //上升沿数据移位

}

return state; //返回读取的数据

}

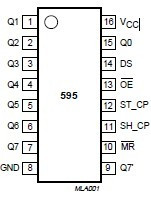

74HC595是一个8位串行输入、并行输出的位移缓存器:并行输出为三态输出。

在SCK 的上升沿,串行数据由SDL输入到内部的8位位移缓存器,并由Q7'输出,而并行输出则是在LCK的上升沿将在8位位移缓存器的数据存入到8位并行输出缓存器。当串行数据输入端OE的控制信号为低使能时,并行输出端的输出值等于并行输出缓存器所存储的值。

74HC595是具有三态输出功能(即具有高电平、低电平和高阻抗三种输出状态)的门电路。输出寄存器可以直接清除。具有100MHz的移位频率。

有一个串行移位输入(Ds),和一个串行输出(Q7’),和一个异步的低电平复位,存储寄存器有一个并行8位的,具备三态的总线输出,当使能OE时(为低电平),存储寄存器的数据输出到总线。

| 符号 | 引脚 | 描述 |

| Q0--Q7 |

第15脚,第1-7脚

|

8位并行数据输出, |

| GND | 第8脚 | 地 |

| Q7’ | 第9脚 | 串行数据输出 |

| /MR | 第10脚 | 主复位(低电平有效) |

| SH_CP | 第11脚 | 数据输入时钟线 |

| ST_CP | 第12脚 | 输出存储器锁存时钟线 |

| /OE | 第13脚 | 输出有效(低电平有效) |

| DS | 第14脚 | 串行数据输入 |

| VCC | 第16脚 | 电源 |

使用方法

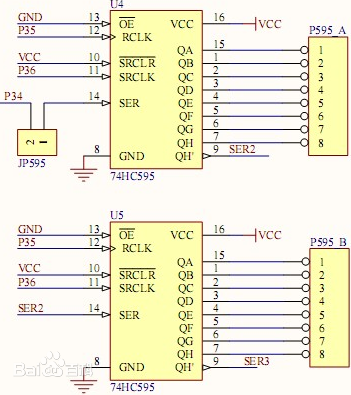

void HC595SendData(unsigned char SendVal){ unsigned char i; for(i=0;i<8;i++) { if((SendVal<<i)&0x80)MOSIO=1; else MOSIO=0; S_CLK=0; NOP(); NOP(); S_CLK=1; } R_CLK=0; NOP(); NOP(); R_CLK=1;}void HC595SendData(unsigned int SendVal){ unsigned char i; for(i=0;i<16;i++) { if((SendVal<<i)&0x8000)MOSIO=1;//setdatalinehigh0X8000 else MOSIO=0; //MOSIO=1 S_CLK=0; NOP(); NOP(); S_CLK=1; } R_CLK=0;//setdatalinelow NOP(); NOP(); R_CLK=1;}14脚:DS(SER),串行数据输入引脚

13脚:OE, 输出使能控制脚,它是低电才使能输出,所以接GND

12脚:RCK,存储寄存器时钟输入引脚。上升沿时,数据从移位寄存器转存带存储寄存器。

11脚:SCK,移位寄存器时钟引脚,上升沿时,移位寄存器中的bit 数据整体后移,并接受新的bit(从SER输入)。

10脚:MR,低电平时,清空移位寄存器中已有的bit数据,一般不用,接 高电平即可。

9 脚 :串行数据出口引脚。当移位寄存器中的数据多于8bit时,会把已有的bit“挤出去”,就是从这里出去的。用于595的级联。

Qx:并行输出引脚

使用参数

VCC:2V~6V,5V最好

I Qn:+- 35mA

注意

第一个从SER送入的bit将会从Q7出去。

74HC595介绍

一张图片和一段文字,哪种信息传递方式给人的第一视觉冲击是最大的?我想大家心中都有答案。

这也是我文章标题的来由。废话就到这里,下面我就用图片来分析595这个chip。

74HC595的最重要的功能就是:串行输入,并行输出。3态高速位移寄存器(好腻害的说)

595里面有2个8位寄存器:移位寄存器、存储寄存器

移位寄存器

在我看来,74HC595的移位寄存器工作方式就像shou qiang弹夹。但是子弹的发射(移位寄存器中的数据转储到存储寄存器),又像是【散x弹】(因为是并行输出嘛)

为什么说和弹夹很像呢?

1、串行输入,已进入的位数据依次下移(所以叫移位寄存器) | 子弹也是一颗一颗上的,先上的子弹,被后上的慢慢往下压。

2、第一个输入的位,是并行输出的最后一个位 | 最先进入弹夹的子弹,最后射出。

74HC595的引脚图

14脚:DS,又叫SER 英文全称是:Serial data input ,顾名思义,就是串行数据输入口。

595的数据来源只有这一个口,一次只能输入一个位,那么连续输入8次,就可以积攒为一个字节了。

假如,我们要将二进制数据0111 1111 输入到595的移位寄存器中,下面来上一张动态图,模拟了前2个位输入的情景。

这个图有7帧,做了很久,毕竟不是做美工的。可谓术业有专攻,闻道有先后啊,还是要虚心学习 :)

0111 1111 这个数据完全输入后是这样的

我们还要注意一个脚:11脚,(shift register clock input) 移位寄存器时钟引脚。上升沿有效。

首先我们要介绍这个引脚的作用。

我们知道51单片机的工作离不开晶振,他使CPU的工作步调稳定有序,就像跑步时喊1,2,1的那个人。

那么这里的位移寄存器时钟也是同样的道理,当一个新的位数据要进来时,已经进入的位数据就在移位寄存器时钟脉冲的控制下,整体后移,让出位置。

上升沿:电平从低到高的那个过程。移位寄存器时钟在上升沿这个过程中才起作用。

存储寄存器

到这里我们已经大致讲了怎么上子弹,也把子弹上齐了。下面来将怎么将子弹打出去,也就是怎么将移位寄存器的数据转移到存储寄存器

存储寄存器是直接和8个输出引脚相通的,将移位寄存器的数据转移到存储寄存器后,Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 就可以接受带到我们

开始输入的一个字节的数据。所谓存储寄存器,就是数据可以存在这个寄存器中,并不会随着一次输出就消失,只要595不断电,也没有新 的

数据从移位寄存器中过来,数据就一直不变且有效。新的数据过来后,存储寄存器中的数据就会被覆盖更新。

12脚: (storage register clock input ) 存储寄存器时钟

数据从位移寄存器转移到存储寄存器,也是需要时钟脉冲驱动的,这就是12脚的作用。它也是上升沿有效。

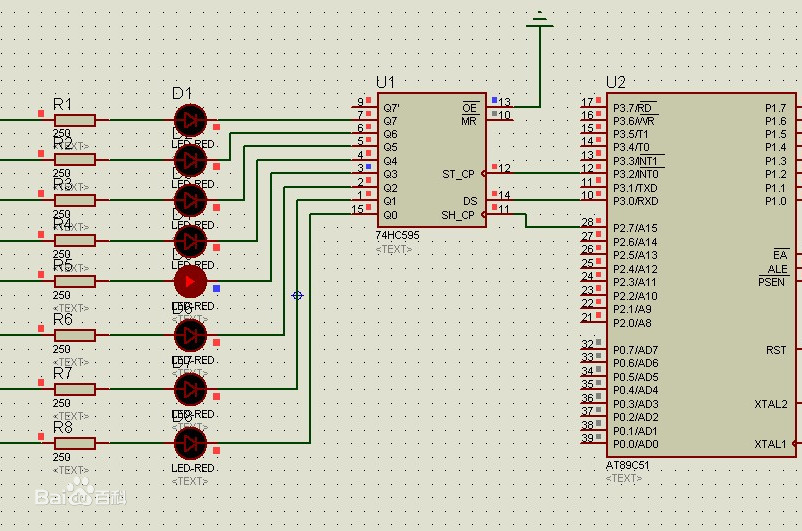

自此,我们已经讲解了一个595正常情况下的工作流程,下面写一个程序,让8个LED保持 亮暗亮暗.... 间隔的效果。

Q0 Q1 Q2 Q3 Q4 Q5 Q6 Q7 分别接 8个LED正极

14脚SER 接 单片机P3.4

11脚SCK 接 单片机P3.6

12脚RCK接 单片机P3.5

13脚OE接GND

10脚MR接VCC

9脚闲置不接

#include<reg51.h> #include<intrins.h> typedef unsigned char uchar; typedef unsigned int uint; /**********函数声明********************/ void SendTo595(uchar byteData);

/***********************************/ sbit SER = P3^4; //p3.4脚控制串行数据输入 sbit SCK = P3^6; //串行输入时钟 sbit RCK = P3^5; //存储寄存器时钟 void main() { SendTo595(85); //85的二进制:0101 0101 while(1); } //功能:发送一个字节的数据给595,再并行输出 void SendTo595(uchar byteData) { char i=0;

for(;i<8;i++) { SER = byteData>>7; //大家自己考量这2句 byteData= byteData<<1; SCK = 1; //上升沿,让串行输入时钟变为高电平,并延时2个时钟周期 _nop_(); _nop_(); SCK = 0; //变为低电平,为下次准备 } /*位移寄存器数据准备完毕,转移到存储寄存器*/ RCK = 1; //上升沿,让存储寄存器时钟变为高电平,并延时2个时钟周期 _nop_(); _nop_(); RCK = 0; }

扩展提升

见识到595的厉害了吧。138译码器通过3个输入口控制8个输出口,而且还只能是特定的8个输出值,

而595只用了一个输入口就可以输任意的8位数据。可谓短小精悍。

啥?你觉的1位控制8位输出还不够?让你的595串联起来吧!打造成加特林机关枪。

在上面的程序中用到的9脚,没用起作用,如果要让2个595串联起来的话,就需要它了。

想一下,我们将移位寄存器的8个位填满后,再往移位寄存器中塞一个会怎么样?也许你想到了。

对!移位寄存器的最后一个位数据会被挤出去,从哪里出去?就是从9脚输出的。如果我们把第一个595的

9脚连接到第二个的串行数据输入脚SER,那么,就形成了595的级联。这样,如果我们用2个595组合成了一个新的超级595,

这个草鸡595的移位寄存器和存储寄存器的容量都翻倍了,1口控制16口,有木有!你还可以继续级联下去!

最后还遗留2个 595 的脚没说

13脚OE 输出使能控制脚,如果它不工作,那么595的输出就是高阻态,595就不受我们程序控制了,这显然违背我们的意愿。

OE的上面画了一条线,表示他是低电平有效。于是我们将他接GND。

10脚MR ,位移寄存器清空脚,他的作用就是将位移寄存器中的数据全部清空,这个很少用到,所以我们一般不让他起作用,他

也是低电平有效,于是我们给他接VCC。

终于写完了,希望帮到大家。以后还会继续讲解其它的74系列的逻辑芯片,尽请期待!

如有错误欢迎指出。 :)