TCL脚本的强大之Modelsim的自动仿真

一设计功能

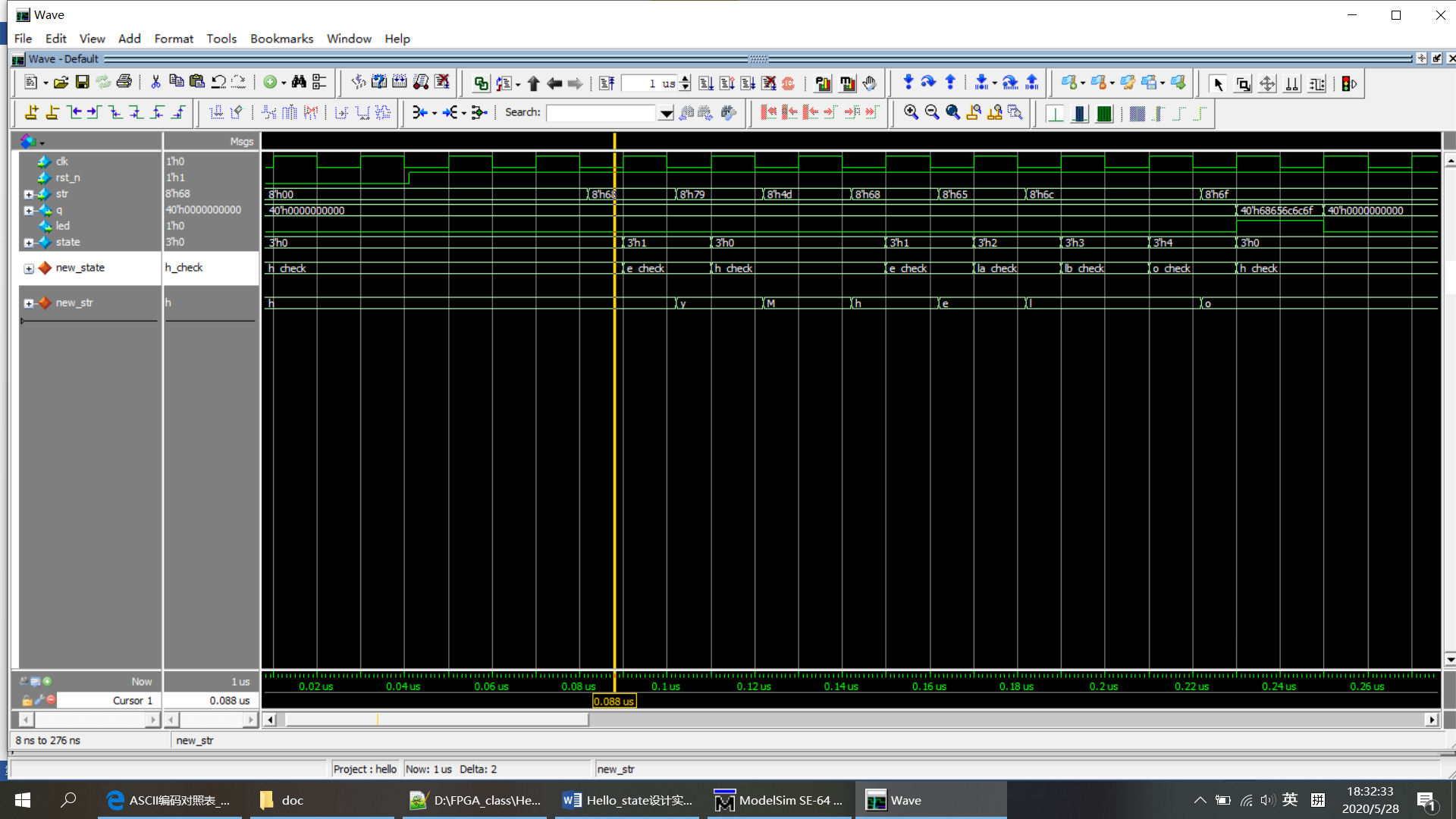

对编写的仿真文件,通过脚本文件TCL能够让输入和输出以我们直观理解的形式在Modelsim仿真软件中显示波形,如本次的设计同时让功能模块的变量state以英文单词和输入str以字母hello等形式在Modelsim中显示波形。

二设计输入

一是hello_state的功能模块,二是hello_state_tb的测试文件,三是TCL的脚本文件。

|

//功能模块代码如下: module hello_state ( clk, rst_n, str, q, led ); input clk; //clock signal input rst_n; input [7:0]str; //the input signal of letter,such as "h" "e " output reg[39:0]q; //the output signal of strings,which is "hello" output reg led; //the output port of led

reg [2:0]state; //the state parameter h_check = 3'd0;//check the letter 'h' parameter e_check = 3'd1; parameter la_check = 3'd2; parameter lb_check = 3'd3; parameter o_check = 3'd4; parameter wait0 = 3'd5;

reg[23:0]delay_cnt; parameter T1MS = 24'd49_999; always@(posedge clk or negedge rst_n)begin if(!rst_n)begin state<=h_check; q<=40'd0; led<=1'b0; end else begin case(state) h_check:begin q<=40'd0; led<=1'b0; if(str=="h")begin state<=e_check; // q<="h"; //two line of code press the display of simulation wave // led<=~led; //more try different ,from zero to one step end else state<=h_check; end e_check:begin if(str=="e") state<=la_check; else state<=h_check; end la_check:begin if(str=="l") state<=lb_check; else state<=h_check; end lb_check:begin if(str=="l") state<=o_check; else state<=h_check; end o_check:begin if(str=="o")begin q<="hello"; led<=~led; state<=wait0; end else led<=led; state<=h_check; end wait0:begin state<=h_check; // if(delay_cnt==T1MS)begin // state<=h_check; // q<=40'd0; // led<=1'b0; // end // else begin // led<=led; // q<=q; // delay_cnt<=delay_cnt+1'b1; // end end default:state<=h_check;

endcase end end endmodule

//测试文件代码如下 `timescale 1ns/1ns `define clock_period 20

module hello_state_tb; reg clk50M; reg Rst_n; reg [7:0]t_str;//be careful the with of t_str same as str wire[39:0]q0; wire rled; hello_state hello_state_m0 ( .clk(clk50M), .rst_n(Rst_n), .str(t_str), .q(q0), .led(rled) );

initial clk50M=0; always#(`clock_period/2) clk50M=~clk50M; initial begin Rst_n=0;t_str=0;#(`clock_period*2+1); Rst_n=1;#(`clock_period*2 + 1); forever begin Rst_n=1; //每个语句注释为ASCII对应的十六进制 t_str="h";#(`clock_period);//8'h68 t_str="y";#(`clock_period);//8'h79 t_str="M";#(`clock_period);//8'h4d t_str="h";#(`clock_period);//8'h68 t_str="e";#(`clock_period);//8'h65 t_str="l";#(`clock_period);//8'h6c t_str="l";#(`clock_period);//8'h6c t_str="o";#(`clock_period);//8'h6f

Rst_n=1;#(`clock_period*5); end

end endmodule

//TCL脚本文件代码如下

quit -sim

.main clear

vlib work vlog ./hello_state_tb.v

vlog ./../rtl/*.v vsim -voptargs=+acc work.hello_state_tb

virtual type { {3'd0 h_check} {3'd1 e_check} {3'd2 la_check} {3'd3 lb_check} {3'd4 o_check} {3'd5 wait0} } abc;

virtual type { {8'h68 h} {8'h79 y} {8'h4d M} {8'h68 h} {8'h65 e} {8'h6c l} {8'h6c l} {8'h6f o} } sin;

virtual function {(abc)/hello_state_tb/hello_state_m0/state} new_state

virtual function {(sin)/hello_state_tb/hello_state_m0/str} new_str add wave /hello_state_tb/hello_state_m0/* run 1us |

三仿真波形

通过波形可以得出结论:成功实现了让state以英文字符串和输入str以英文字母在Modelsim中显示出波形,利于我们观察和分析设计的逻辑。

浙公网安备 33010602011771号

浙公网安备 33010602011771号