CSAPP 第六章 存储器层次结构

6-1 存储技术

Random Access Memory(随机访问存储器)

- Static RAM(Cache)

- Dynamic RAM(内存)

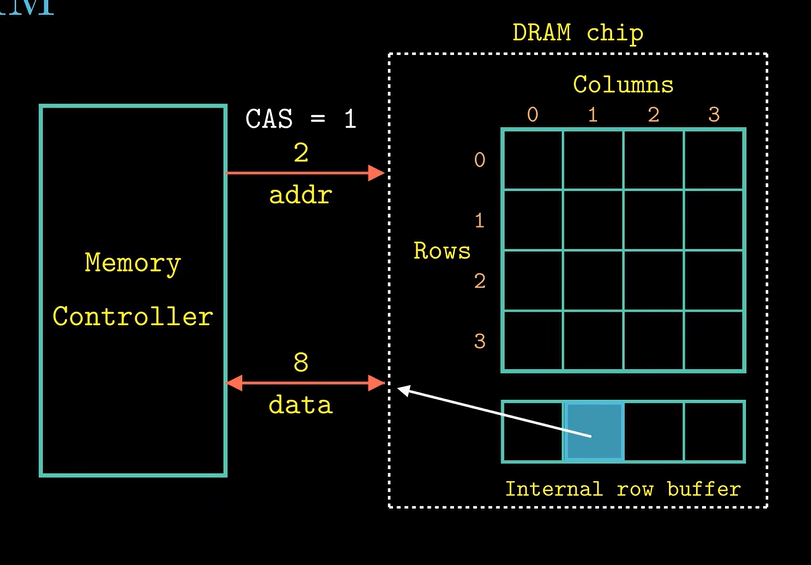

DRAM

二维是为了降低chip(芯片)上地址引脚的数量。

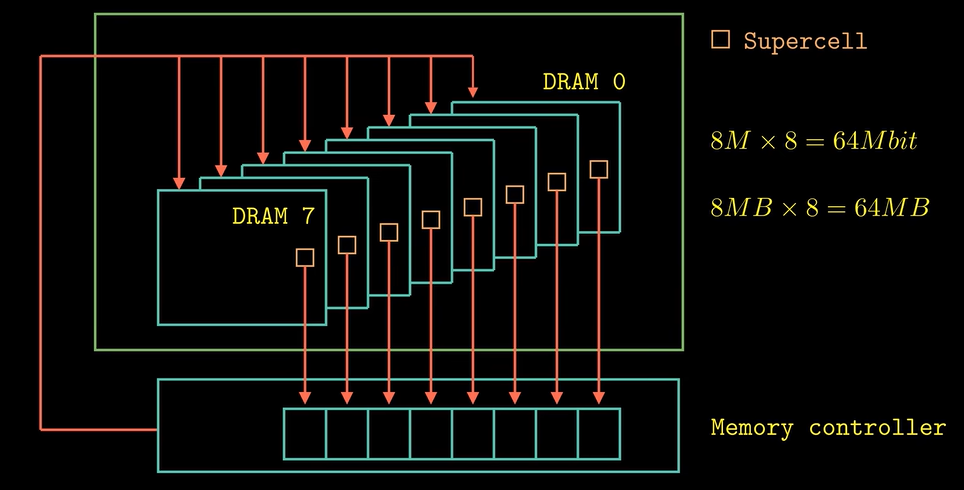

DRAM construct 的内存模块

6-2 机械磁盘

SRAMs/DRAMs:

I/O device:

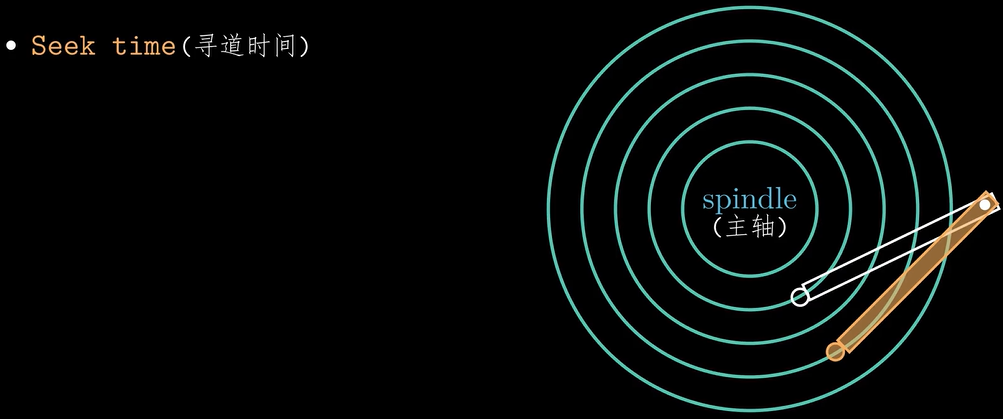

寻道

T=9ms

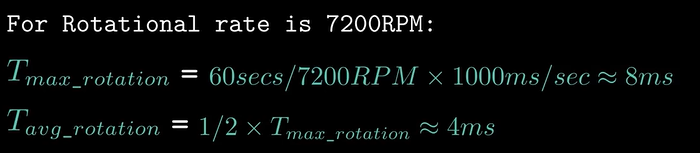

旋转

传送

T=0.02ms

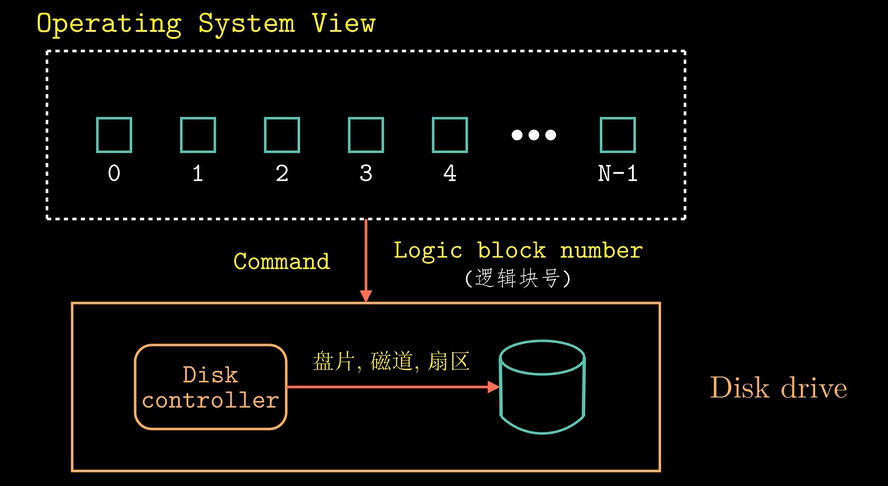

操作系统的视角

6-3 固态硬盘/局部性

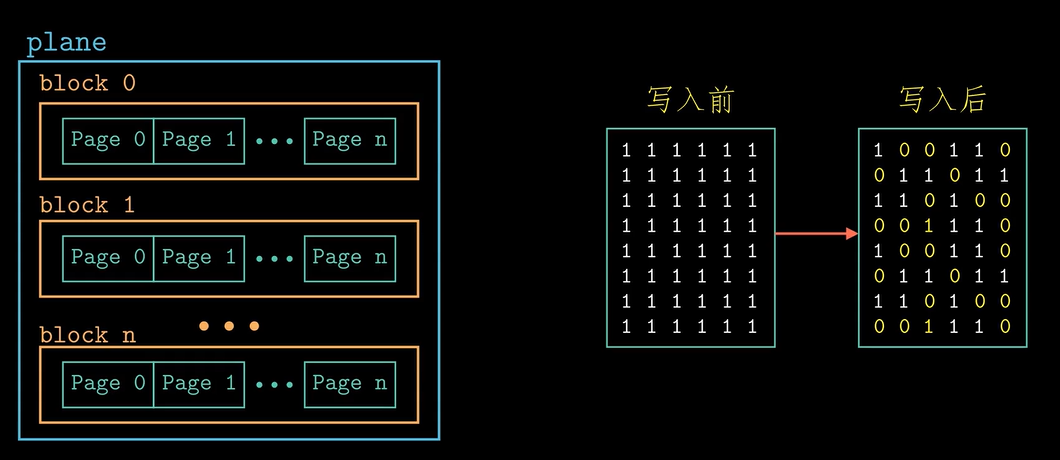

固态硬盘

不可以直接覆盖,必须得擦除。

局部性

6-4 存储器的层次结构

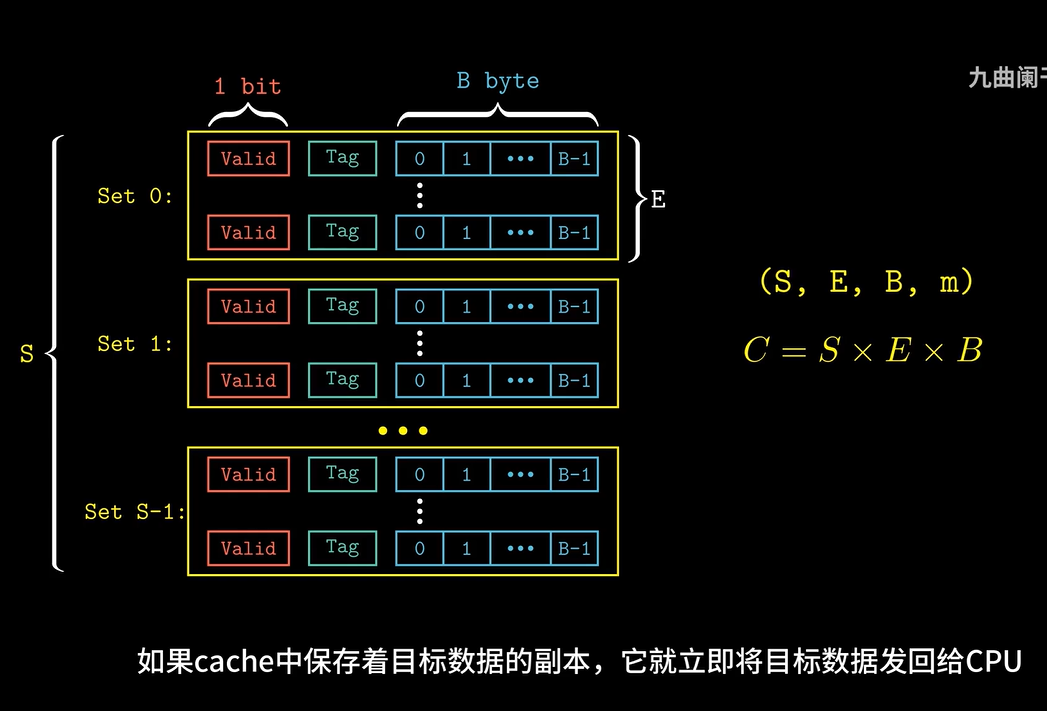

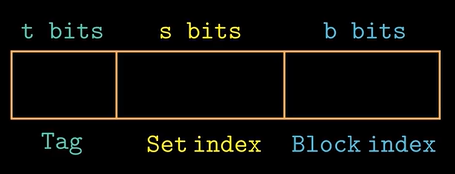

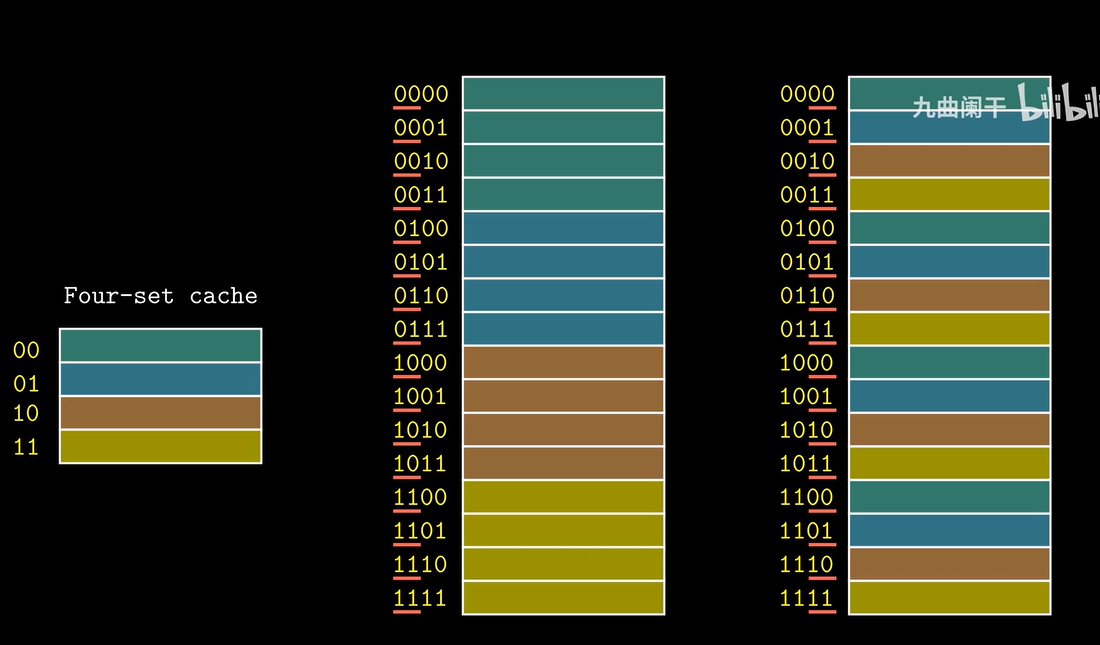

用低位做索引的原因

用高位做索引,cache的使用率太低了(若空间局部性良好的话),如图所示

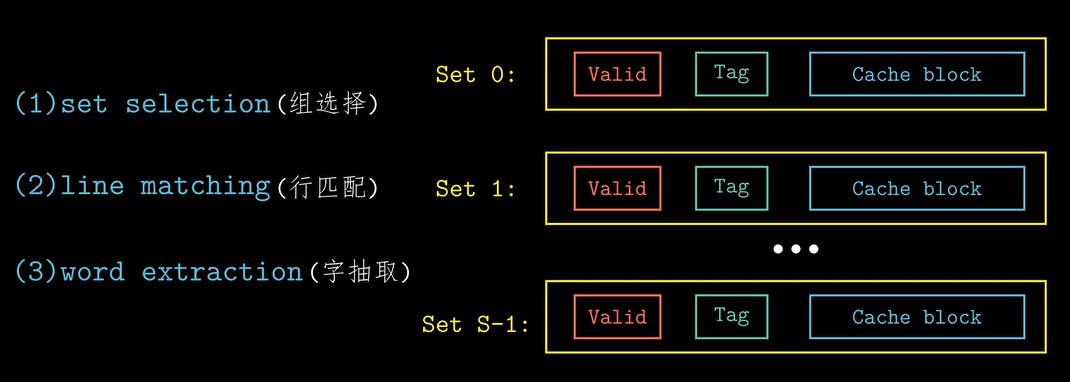

6-5 直接映射高速缓存

即Line=1的情况

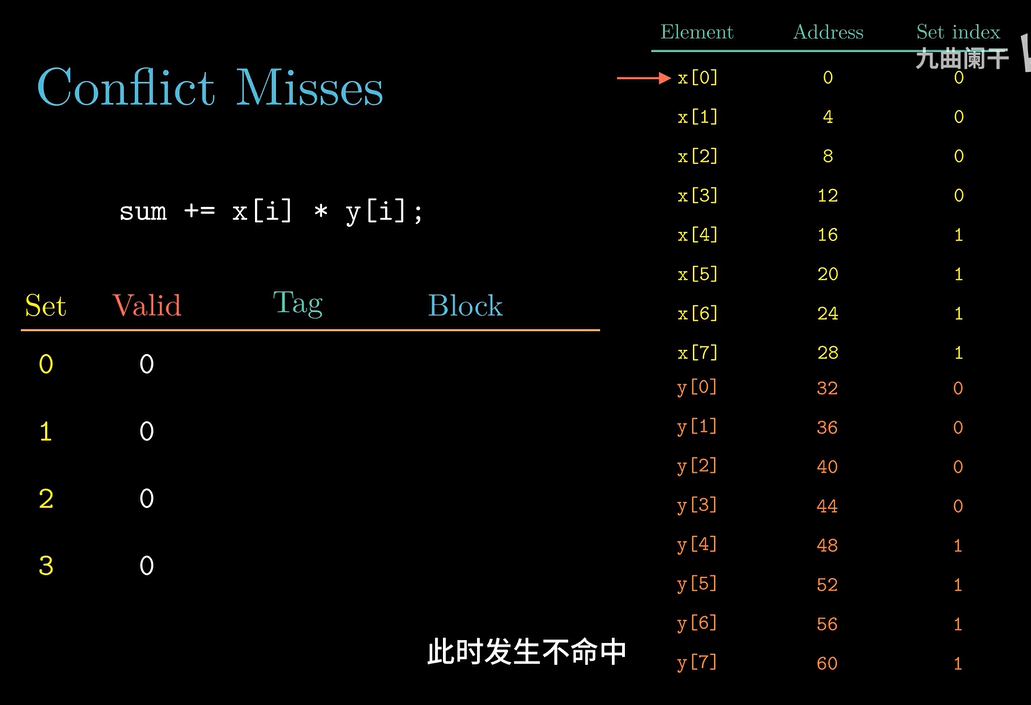

Conflict Misses

抖动

解决方案:改变数组大小

6-6 组相联/全相联高速缓存

替换策略

写入策略

写穿透:缓存+主存 写不分配:直接往内存写

写回:缓存 写分配:从内存加载到cache中,再往cache写。

块大小的影响

块越大,对空间局部性好的好,行越少,对时间局部性好的命中率就会受到损害,因为会反复加载。

cache line的影响

cache line 越多,抖动现象发生的几率就越低。相联度越高,实现的复杂度就高,访问速度难提高。

写策略的影响

L1L2 一般使用写穿透,越往下写回越多。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· winform 绘制太阳,地球,月球 运作规律

· AI与.NET技术实操系列(五):向量存储与相似性搜索在 .NET 中的实现

· 超详细:普通电脑也行Windows部署deepseek R1训练数据并当服务器共享给他人

· 【硬核科普】Trae如何「偷看」你的代码?零基础破解AI编程运行原理

· 上周热点回顾(3.3-3.9)