流水线的相关问题

引言

在CPU流水线中会出现一些相关的情况,导致流水线不能很好地表现出理论性能

流水线相关分类

结构相关

指的是在指令执行过程中,由于硬件资源满足不了指令执行的要求,发生硬件资源冲突而产生的相关

例子:指令和数据使用同一个存储器,如果取指的同时需要对存储器中的数据进行访问,产生存储器访问冲突

控制相关

指的是流水线中的分支指令或者其他需要改写PC的指令造成的相关

数据相关

指的是在流水线中执行的几条指令中,一条指令依赖于前面指令的执行结果

tips:下面的指令j都是在指令i后面执行,且二者对同一个寄存器或存储器单元操作

RAW

即指令j在指令i写入寄存器之前尝试读出该寄存器的内容,指令j得不到正确的数据

WAR

即指令j在指令i读取寄存器之前就去更改寄存器的内容,指令i得不到正确的数据

WAW

即指令j在指令i之前写寄存器,指令'i'的值会覆盖指令j的值,寄存器保存的数据不是最新的

解决办法

数据相关

WAW

合理分配写入的时机,最好确保只有一个阶段进行写入操作 --- 目前我只知道这个办法

WAR

和WAW类似,控制读写的阶段,将二者分开,比如:每次都是在译码阶段读寄存器,在回写阶段写寄存器

RAW

-

插入暂停周期

当检测到该数据相关插入nop周期 --- 一定程度上会影响流水线的效率 -

编译器调度

软件调整指令执行的顺序 -

数据前推

将计算结果从其产生处直接送到其他指令需要处或所有需要的功能单元处,避免了流水线的暂停

控制相关

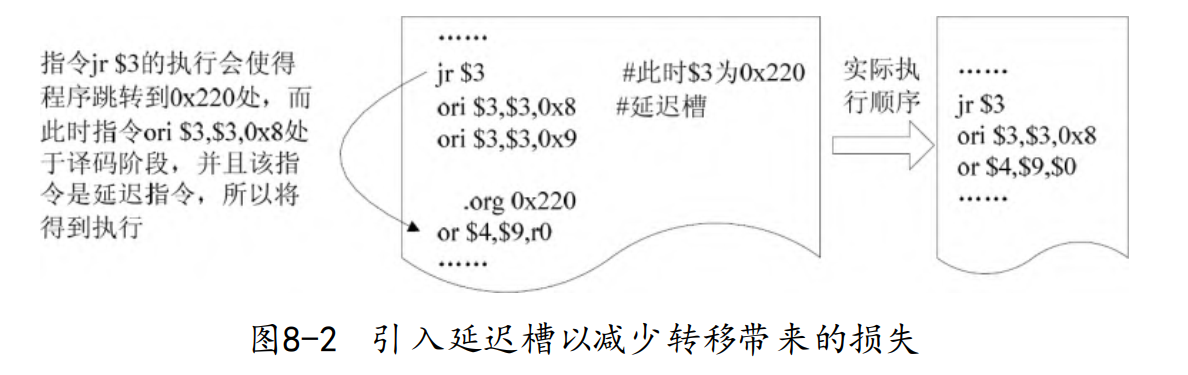

使用延迟槽技术,即转移指令后面的一条指令为延迟指令,延迟指令一定会执行,但是结果不一定会被保存

选自雷思磊的《自己动手写CPU》

同时,将分支跳转提前到译码阶段,即在译码阶段就完成对跳转指令的执行,因为跳转指令只需要改变PC的值

浙公网安备 33010602011771号

浙公网安备 33010602011771号