2.3-AHB(传输)

资料来源

(1) amba bus spec翻译.pdf

(2) ARM各种Memory类型理解_谷公子的博客-CSDN博客_arm memory [未阅]

(3) ARMv8官方手册学习笔记(十二):Device memory - 知乎 (zhihu.com) [未阅]

(4) Cacheable VS Non-Cacheable_亦大乐谍的博客-CSDN博客 [未阅]

(5) Cache写机制:Write-through与Write-back_skate的博客-CSDN博客_write-back [未阅]

3.传输

3.6等待传输

(1) slave需要更多时间提供或采样数据,将使用HREADYOUT信号插入等待状态; 在等待状态中,master只能改变传输类型(HTRANS)和地址;

3.6.1等待状态传输类型改变

(1) slave正在请求等待状态,master不能改变传输类型,除非空闲传输或者固定长度突发传输的忙传输BUSY或者未定义长度突发传输的忙传输;

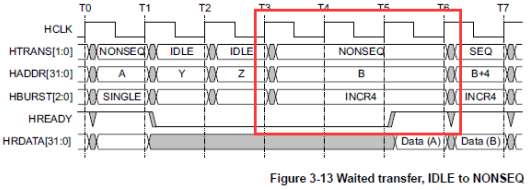

(2) 空闲传输:在等待状态中,master允许将空闲状态IDLE转为非连续传输NON-SEQ;当HTRANS传输类型改为NON-SEQ,master必须保持HTRANS不变,直至HREADY信号为高电平;

注1:T1-T2,master插入地址为Y的空闲传输,slave将HREADY拉低请求等待状态;

注2:T2-T3,master插入地址为Z的空闲传输;

注3:T3-T4,master将传输类型改为NON-SEQ,使用增量为4,初始地址为B的突发传输;

注4:T4-T6,master需要保持HTRANS不变;

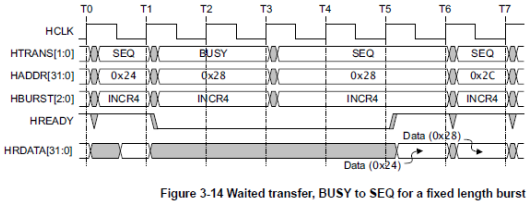

(3) 固定长度的突发传输中的忙传输:这种情况下,master可以将类型由BUSY变为SEQ;当HTRANS变为SEQ后,master必须保持HTRANS不变直至HREADY信号为高电平;

注1:T1-T3,master在地址0x28处插入忙传输,slave拉低HREADY插入等待状态;

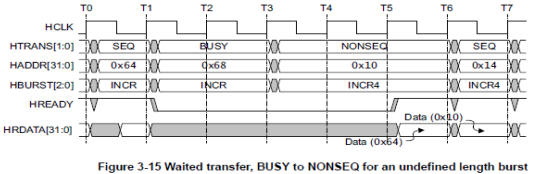

(4) 未定义长度的突发传输中的忙传输:这种情况下,当HREADY为低电平时,master可以将传输类型改为任何其他的传输类型;如果改为SEQ,则继续突发传输,改为IDLE或者NONSEQ,则终止突发传输;

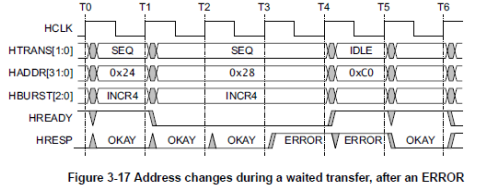

3.6.2等待状态地址改变

(1) 当slave正在请求等待状态,master只可以改变与一次地址,除非在一次空闲传输或者一个错误响应后;

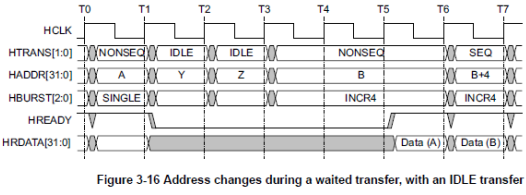

(2) 在空闲传输中:在一个等待传输中,master允许改变地址;当HTRANS改为NONSEQ后,master必须保持地址不变直至HREADY为高电平;

注1:在T1-T2,master插入空闲传输IDLE,slave将HREADY拉低插入等待状态;

注2:T5-T6,单次突发传输结束,地址A数据完成,master开始地址B的第一拍,也就是地址阶段; T6-T7,地址B数据完成并开启下一拍;

(3) 在错误响应后:如果slave发出ERROR响应,当HREADY为低电平时,master允许改变地址;

注1:T4-T5,slave回复ERROR;在T4-T5,master将传输类型改为IDLE;T4,slave回复ERROR且HREADY为低电平,master将地址改变为0xc0; T5,slave完成0x28的ERROR响应; T5-T6,slave完成地址0xc0的响应;

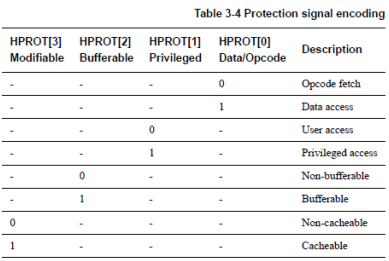

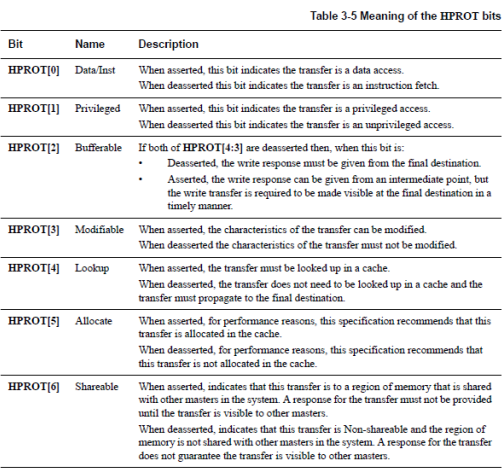

3.7保护控制protection control

(1) 保护控制信号HPROT提供总线访问的额外信息,主要用于实现一些级别的保护;

(2) HPROT表明传输时一次取指令或者数据访问,是特权模式还是普通用户模式;对于有内存管理单元mmu的master,这些信号还表明当前访问时cacheable的还是bufferable的;

(3) HPORT控制信号和地址总线有一样的时序,但在整个突发传输中,它们必须保持不变;

3.8 存储器类型

3.8.1数据或指令

(1) 所有传输都包含HPROT[0],该位有效表明是数据传输,失效则是取指操作;

(2) 规范推荐将该位设为高电平,除非已知是一次指令获取;

3.8.2 非特权或特权

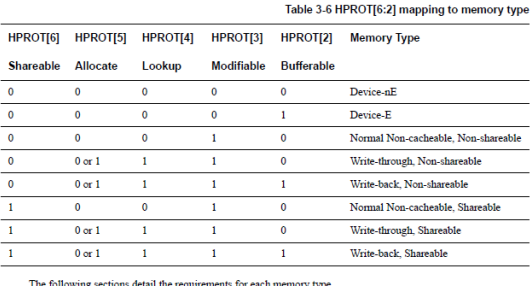

3.8.3 存储器类型

(1) 下表中未列举的组合是不允许出现的;

3.8.4设备存储device memory要求

(1) Device-E可以提前应答;

(2) Device-nE必须最终目标应答;

注1:读数据必须从最终目标中获得;

注2:传输不能拆分或合并;

注3:读不能预读取prefetched或随机执行;

注4:写不能合并;

注5:来自同一个master和slave的所有传输必须保持有序;

3.8.5常规存储normal memory要求

(1) non-cacheable memory;

(2) write through & write back;

浙公网安备 33010602011771号

浙公网安备 33010602011771号