复杂多维数组

资料来源

(1) Verilog系列:【11】敏感信号列表中的数组 (qq.com)

(2) jerry ic 验证;

1.复杂多维数组

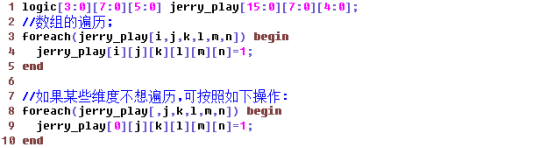

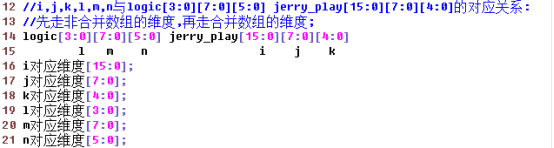

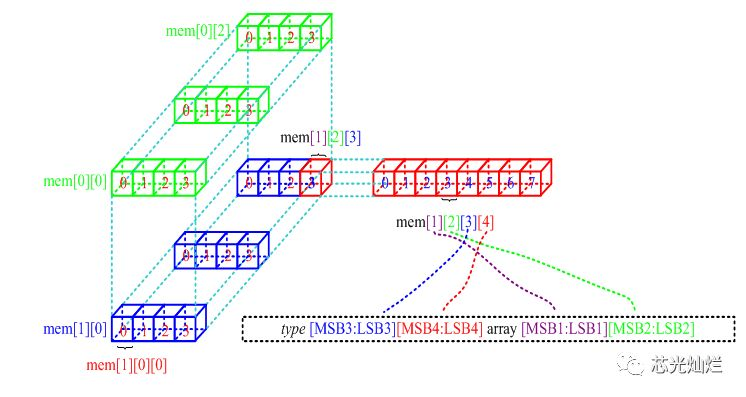

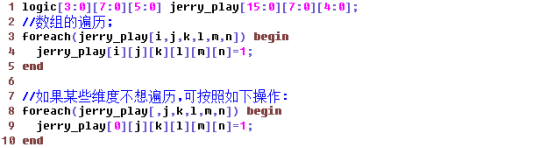

(1) 示例:

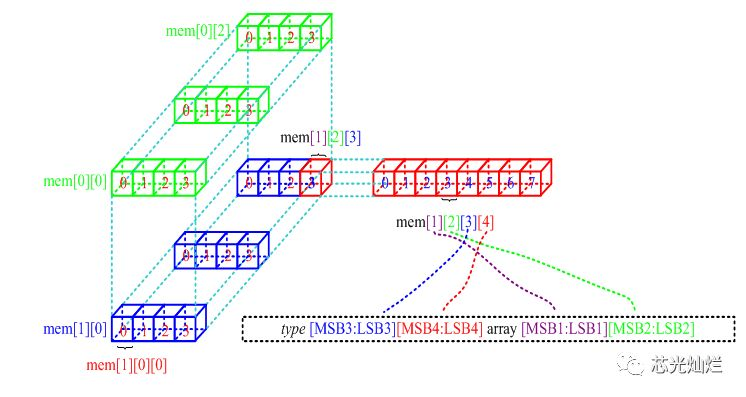

type [MSB3:LSB3][MSB4:LSB4] array [MSB1:LSB1][MSB2:LSB2]

reg [0:3][0:7] mem[0:1][0:2]

(2) 示例:

(1) Verilog系列:【11】敏感信号列表中的数组 (qq.com)

(2) jerry ic 验证;

(1) 示例:

type [MSB3:LSB3][MSB4:LSB4] array [MSB1:LSB1][MSB2:LSB2]

reg [0:3][0:7] mem[0:1][0:2]

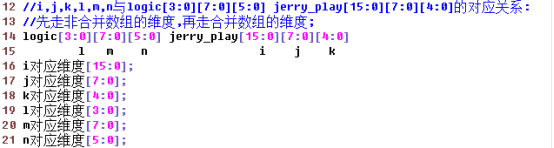

(2) 示例: