验证覆盖率及用仿真工具收集覆盖率(code cov/func cov)

资料来源

(1)公众号-芯片学堂;

(2)VCS user guide;

(3)面试系列:RTL基本知识【1】关于coverage (qq.com)

(4) Verdi Coverage User Guide and Tutorial (手册是信息源头)

1.验证覆盖率

(1)验证覆盖率只是为了证明验证是否已经完成;

(2)验证覆盖率达标不能说明验证是完备的,但验证覆盖率不达标说明验证很有可能是不完备的;

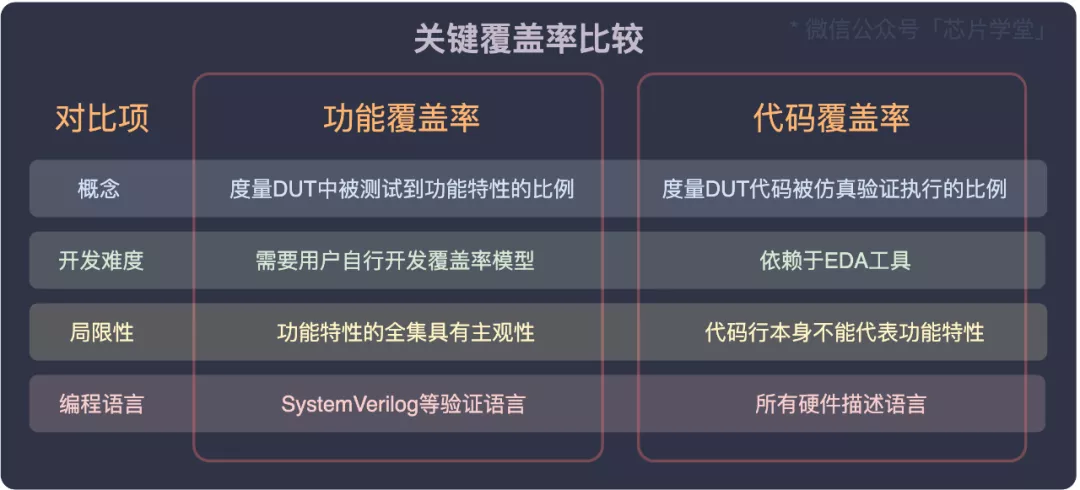

(3)验证覆盖率指标包括功能覆盖率(function coverage)和代码覆盖率(code coverage);

(3.1)100%代码覆盖率+低于100%的功能覆盖率->验证不完整;

(3.2)低于100%代码覆盖率+100%功能覆盖率->代码冗余或验证计划有误(可能未对所有的功能特性编写覆盖点);

1.1功能覆盖率(user defined/用户自定义)

(1)作用:用于度量DUT中哪些功能或者特性被测试用例测试到;

(2)实现:使用sv等验证语言实现覆盖率模型(coverage model)或断言(assertion),并从大量的回归测试(regression)中采集覆盖数据(sample),然后进行统计数据的合并(merge),最后做覆盖率分析(analysis);

(3)侧重点:模块验证会更关心是否所有的功能都被触发,而系统验证会更关心是否耦合了各类工作场景;

(4)涉及点:sv功能覆盖率模型的实现,需要用到covergroup和coverpoint;

1.2代码覆盖率(仿真工具生成)

(1)分类:翻转覆盖率(toggle cov),行覆盖率(line cov),语句覆盖率(statement cov),分支覆盖率(branch cov),状态覆盖率(FSM cov);

(2)作用:通过对代码覆盖率的分析,可以较容易发现RTL中冗余的代码块,这种冗余的代码块可能来自于RTL实现逻辑的错误,或者验证计划不够完备;

(3)收集:由EDA工具在启用相应功能的选项之后自动化完成,不需要工程师开发额外的代码;

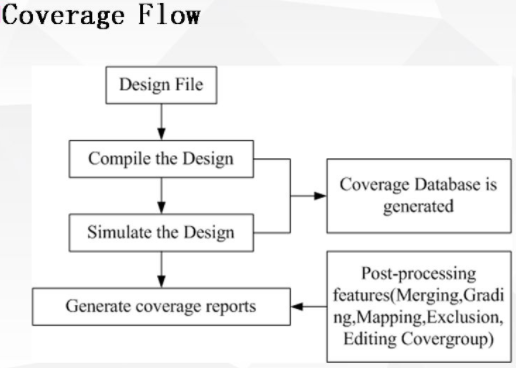

2.验证覆盖率的收集

2.1code coverage

(1)通过在编译和仿真时,添加-cm line+tgl+branch+cond+fsm+assert收集(需要补充-cm_hier option的使用);

注1:要在编译和仿真时都添加,而不是仅仅编译时,或仅仅仿真时;

编译:

vcs -P $VERDI_HOME/share/PLI/VCS/LINUX/novas.tab \

$VERDI_HOME/share/PLI/VCS/LINUX/pli.a \

-f file_list.vc -cm line+tgl+fsm+cond+branch+assert -sverilog

仿真:

./simv -cm +line+tgl+fsm+cond+branch+assert

注2:如果design包含用于power simulation的UPF文件且如果使能VCS power coverage feature,那么在编译时,需要额外添加编译option: -power=coverage+dump_hvp;

注3:用verdi查看覆盖率信息vdb时,采用verdi -cov -covdir *.vdb,注意一定要包含编译目录下的vdb和仿真目录下的vdb;如果仅仅打开编译目录下的vdb,没有任何覆盖率信息;如果仅仅打开仿真目录下的vdb,则报"Error: design not load yet.";

2.2function coverage

(1)通常用define限制打开或关闭,在编译时,添加相应的define即可,如+define+COVERAGE_ON;

注1:功能覆盖率会自动收集,但验证前期可能不关注覆盖率,所以通常会有开关控制功能覆盖率的收集;

浙公网安备 33010602011771号

浙公网安备 33010602011771号