17-SVA中的多时钟定义,matched构造,expect构造

资料来源

(1) 硅芯思见:【94】SVA中的multi-clock (qq.com)

(2) 硅芯思见:【90】SVA中的序列表达式操作符 (qq.com)

1.SVA中的多时钟定义

(1) SVA允许序列或者属性使用多个时钟定义来采样独立的信号或者子序列;

(2) SVA会自动地同步不同信号或者子序列使用的时钟域;

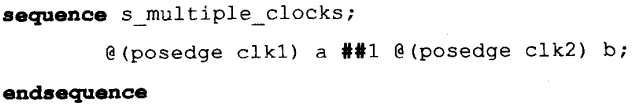

(3) 当在一个序列中使用多个时钟信号时,只允许使用##1延迟构造。

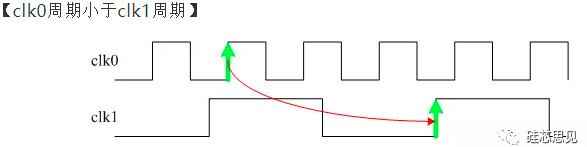

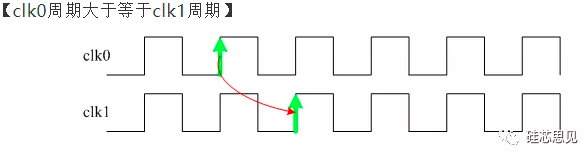

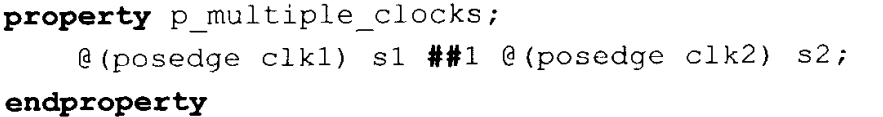

注1:下图所示sequence-s_multiple_clocks检验在时钟clk1的任何上升沿,信号a为高,接着在时钟clk2的上升沿,信号b为高.

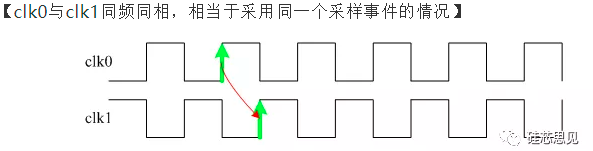

下幅图片中有错误,clk0与clk1同频同相改为同频;

注2:##1延迟构造将检验时间移到时钟clk2的最近的上升沿,检查信号b是否为高.

(4) 当在一个序列中使用多个时钟信号时,不允许使用##0或##2.

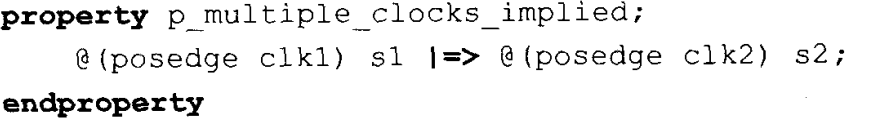

(5) 当在一个属性中使用多个时钟信号时,属性可以在序列定义之间使用非交叠蕴含运算符;

(6) 当在一个属性中使用多个时钟信号时,禁止在不同时钟驱动的序列间使用交叠蕴含运算符;

2.matched构造

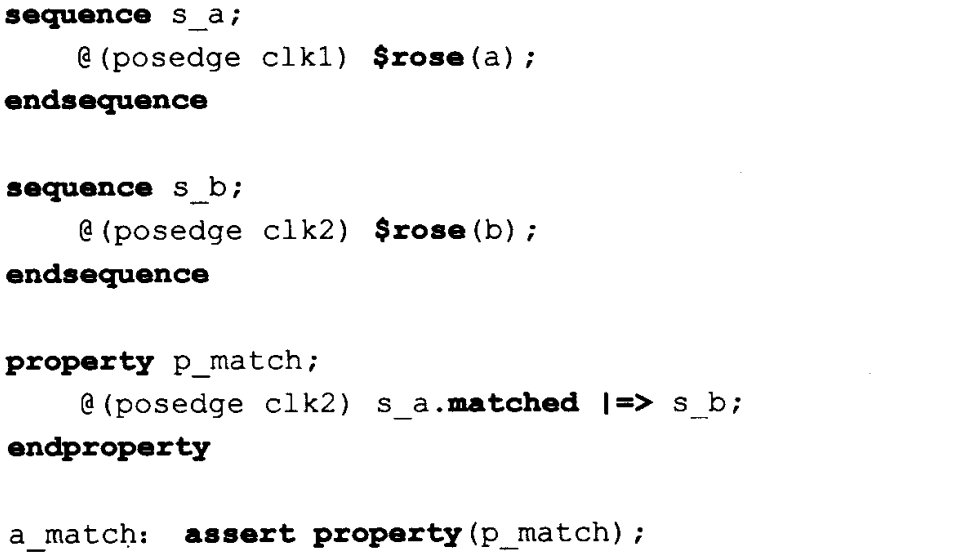

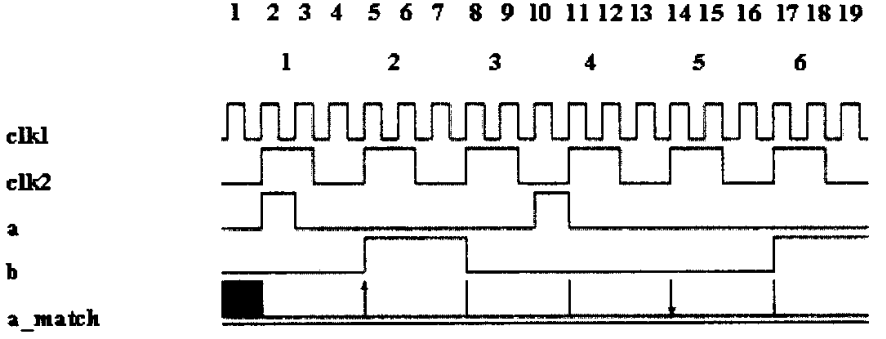

(1) 任何时候如果一个序列定义了多个时钟,构造"matched"可以用来检测第一个子序列的结束点.

(2) 下图所示property中,序列s_a查找信号a的上升沿,但是信号a是根据时钟clk1来次啊应的; 序列s_b查找信号b的上升沿,信号b是根据时钟clk2来采样;

属性p_match验证在给定的时钟clk2的上升沿,如果序列s_a匹配,那么在一个周期后,序列s_b也必须为真.

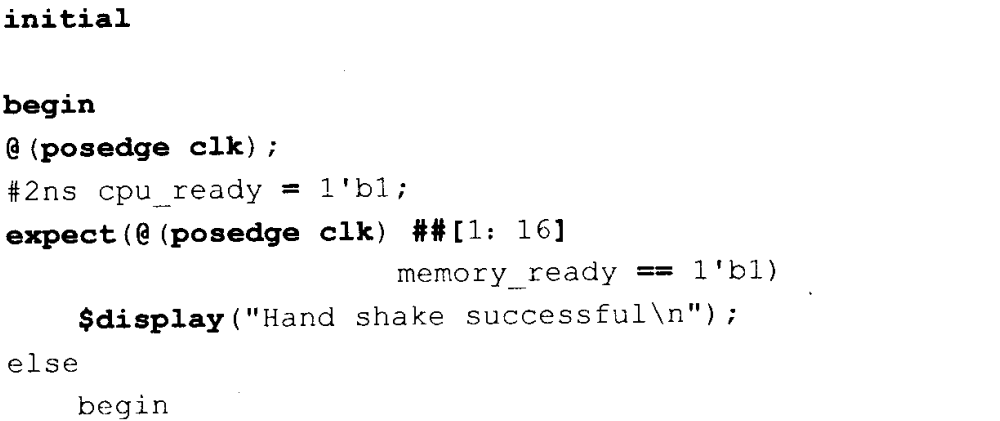

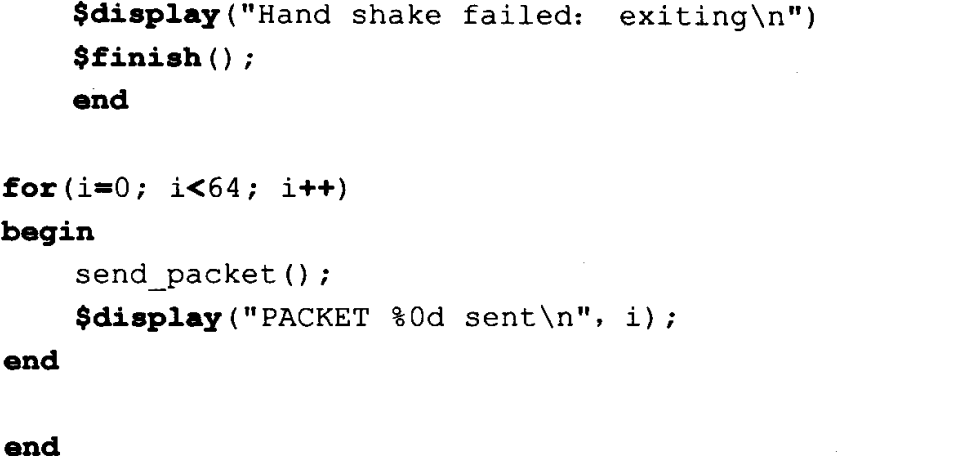

3.expect构造

(1) SVA中的expect构造与verilog中的等待构造相似,区别在于expect语句等待的是属性的成功检验;

(2) expect构造后面的代码是作为一个阻塞的语句来执行. expect构造的语法与assert构造相似; expect语句允许在一个属性成功或者失败后使用一个执行快;

浙公网安备 33010602011771号

浙公网安备 33010602011771号