vcs与verdi单步调试, vcs ucli调试hang【IMP】

资料来源

(1) VCS与verdi联合进行单步调试 | 骏的世界 (lujun.org.cn)

(2) 当simulation hang住的时候该怎么办? (qq.com)

(3) https://blog.csdn.net/gsjthxy/article/details/107207452

注1:(1)中的单步调试不是很适合debug hang case; (2)中的方法,试用了一下,首先tcl脚本存在一些语法问题,需要注意空格的必要性;其次,改掉语法错误后,调用函数没有效果;(3)和(2)原理上一样,具体实现不同;

1.VCS与verdi联合进行单步调试

注:资料(1)中的示例可以把testbench中的一些变量拖到波形中观察!!!

(1) 编译: 在VCS编译的时候,要额外加上 -debug_access+all -kdb -lca 这个三个选项参数。这样,之后生成的simv,才能支持单步调试功能。

即 vcs -debug_access+all -kdb -lca

(2) 编译示例: makefile的vcs目标,对代码进行编译,生成simv。

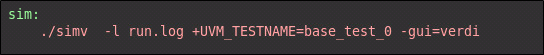

(3) 仿真: 生成simv后,要增加一个选项,-gui=verdi,表示使用verdi这个工具进行单步调试。

(4) 仿真示例: makefile的sim目标,代码仿真,进行单步调试。

(5) gui界面:执行 make vcs; make sim 后,会弹出verdi界面,并且停在0时刻。此时打开波形,时刻停在0时刻,信号还没有产生波形。

(5.1) 在关心的代码处设置断点。

(5.2) 在交互式窗口,输入run,或者快捷键F5,或者菜单栏Simulation->Run/Continue。运行仿真。

(5.3) 仿真会在断点处停下来。

(5.4) 在交互式窗口输入next,或者快捷键F10,或者菜单栏 Simulation->Step/Next->Next。

浙公网安备 33010602011771号

浙公网安备 33010602011771号