2.1-AHB(简介与信号描述)

资料来源

(1) AHB总线协议(一)_weixin_33875839的博客-CSDN博客 【未阅】

(2) AHB_百度百科 (baidu.com)【未阅】

(3) AHB总线协议(一) - 迈克老狼2012 - 博客园 (cnblogs.com) 【未阅】

(4) AHB总线协议(二) - 迈克老狼2012 - 博客园 (cnblogs.com) 【未阅】

(5) AHB总线系列学习(一) - 程序员大本营 (pianshen.com) 【未阅】

(6) amba bus spec翻译.pdf

(7) AXI总线的Burst Type以及地址计算 | WRAP到底是怎么一回事?_Ericcoding的博客-CSDN博客【未阅】

(8) AHB总线规范详解.pdf

注1:注意AHB与AHB Lite的区别;

注2:该系列文章还不够全面,关于slave插入等待,仅涉及到了HREADY拉低这种短等待,没提到RETRY与SPLIT长等待;

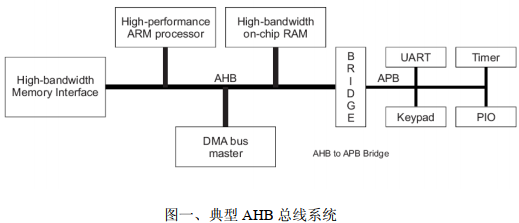

1.介绍

(1) AHB(Advanced High-performance Bus)用于高性能、高时钟频率的系统结构,典型的应用如ARM核与系统内部的高速RAM, Nand Flash, DMA, Bridge的连接;

(2) APB(Advanced Peripheral Bus)用于连接外部设备,对性能要求不高,而考虑低功耗问题;

(3) ASB(Advanced System Bus)(用处??);

1.1关于协议

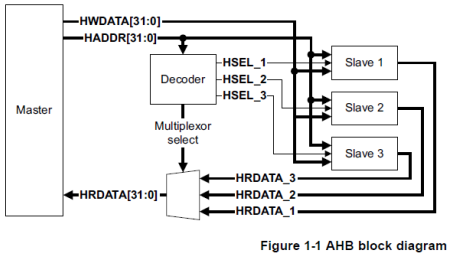

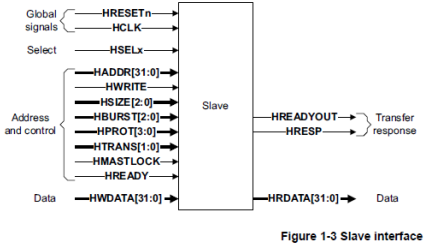

(1) 单master设计: 译码器监测master提供的地址,选择正确的slave;复用器的输出将相应的slave数据反馈给master;

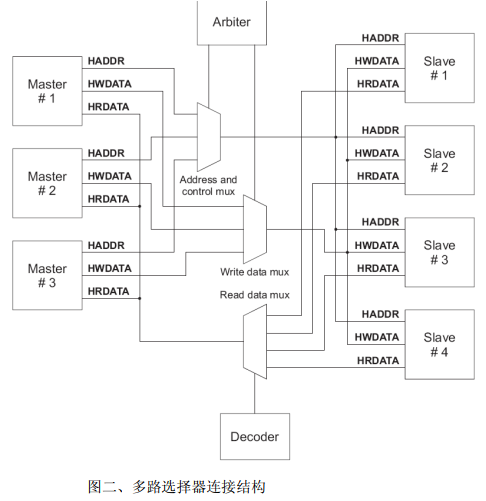

(2) 多master设计:需要使用互连组件提供仲裁决定谁占用总线,路由从不同master到合适slave的信号;

注1:AHB总线系统有master, slave, arbiter, 数据多路选择器(写数据与读数据分别由对应的选择器),地址控制信号多路选择器, 译码器;

注2:有需要占用总线的master向arbiter提出占用总线请求,arbiter授权给指定master; 任一时间周期只有一个master可以接入总线,对其指定的slave进行读写操作;

注3:arbiter将获得授权的master信息传递给地址控制信号多路选择器以及读写数据多路选择器,以选择哪个master接入总线;

注4:总线统一规划slave的地址,译码器根据master需要访问的地址选择哪个slave与master进行数据通信;

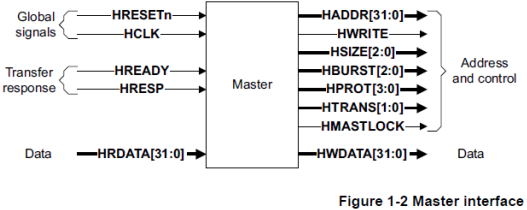

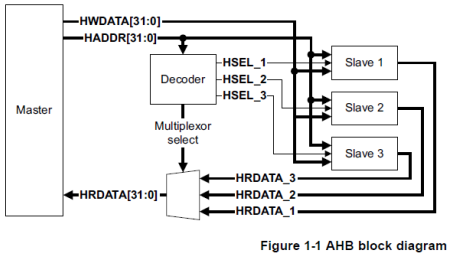

(3) master接口:提供地址和控制信息用于读写操作;

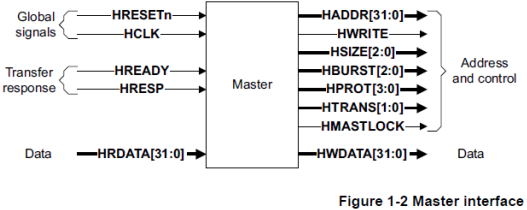

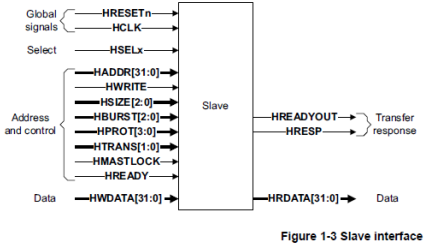

(4) slave接口:slave响应master发起的传输,使用HSELx选择译码器发出的信号,来控制什么时候响应总线传输,相当于片选; slave需要反馈一些信号,表明总线传输完成或延展(即目前不能传输完,需要增加时间完成),传输成功还是失败;

(5) 互连interconnect: 互连组件提供master和slave之间的连接;单master系统只需要译码器和复用器mux;多master系统需要仲裁谁占用总线和信号路由(地址,控制和写数据信号都需要路由);

(6) 译码器:解析每次传输的地址(HADDR),提供选择参与传输slave的信号(HSEL_*),还提供复用器的控制信号,也就是选择对应slave的输出信号(HRDATA);

(7) 复用器:slave到master的复用器需要复用读数据总线和slave的响应信号,即从多个slave的读出数据和响应中选择合适的反馈给master,一次传输只进行一个master和slave的数据传输;

1.2操作

(1) master通过驱动地址和控制信号发起一次传输,这些信号表明传输地址,读或写,传输位宽和是否是突发传输的一部分;

(2) 传输可以是单次的,也可以是地址等大增加的突发传输(incrementing burst),还可以回环突发(wrap burst);

(3) 写数据总线将数据从master移向slave,读数据总线将数据从slave移向master;

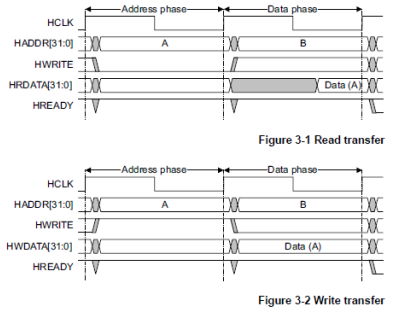

(4) 每次传输包含地址阶段(address phase) (即一个地址和控制周期)和数据阶段(data phase)(一个或多个周期用于数据传输);

(5) slave不能提出地址阶段需要扩展的请求(master可以通过BUSY状态延迟地址阶段),也就是地址信号需要再处理,因此所有的slave必须能够在地址阶段采样地址信息;

(6) slave可以通过使用HREADY信号提出扩展数据阶段的请求,也就是没准备好,需要等待,HREADY允许slave有额外的时间准备采样数据(HREADY信号是由复用器传递给master,单复用器的HREADY信号则源于slave的HREADYOUT信号);

(7) slave使用HRESP信号表示一次传输的成败;

2.信号描述

2.1 master信号

(1) HADDR:发往slave和decoder,32位系统地址总线;

(2) HBURST:发往slave,该值表示突发传输是单次的还是一次突发传输的一部分;

(3) HMASTLOCK:???发往slave;

(4) HPROT:发往slave,该信号指出传输是取指令还是数据访问,传输是特权模式还是用户普通模式;(当extended_memory_types特性为true时,HPROT[6:4]起作用);

(5) HSIZE:发往slave,指出传输的大小,也就是字节byte,半字节half-byte,字word;

(6) HNONSEC:发往slave和decoder,指出传输是安全的,还是不安全的(在secure_transfers为true时,支持该信号);

(7) HEXCL:发往互斥访问监视器,???

(8) HMASTER:发往互斥访问监视器和slave,master标识符; 互连组件确保每个master有独一无二的标识(exclusive_transfers为true时才支持);

(9) HTRANS:发往slave,指出当前传输是idele, busy, non-sequential还是sequential;

(10) HWDATA:发往slave,写数据总线;

(11) HWRITE:发往slave,指出传输方向,高电平表示写,低电平则表示读,与地址信号有一样的时序,但在突发传输中需要保持不变;

2.2 slave信号

(1) HRDATA:发往复用器,在读操作中,读数据总线传输选中slave的数据到复用器,复用器然后将数据传至master;

(2) HREADYOUT:发往复用器,高电平表示传输完成,低电平可以扩展一次传输;

(3) HRESP:发往复用器,低电平表示传输没问题,高电平表明传输出错;

(4) HEXOKAY:发往复用器,表明互斥传输exclusive transfer成功还是失败;

2.3 译码器信号

(1) HSELx:发往slave,用于找到master需要的slave(每个slave都有自己的选通信号);

2.4 复用器信号

(1) HRDATA:发往master,由译码器选择;

(2) HREADY:发往master和slave,高电平表示前面的传输已经完成,由译码器选择合适的slave的HREADYOUT信号;

(3) HRESP:发往master,由译码器选择合适的slave的HRESP信号;

(4) HEXOKAY:发往master,由译码器选择;

3.传输

3.1基本传输

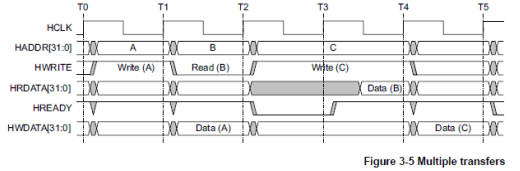

(1) 最简单的传输不包含等待状态,一次传输由地址及控制信号阶段与数据阶段组成;

注1:HCLK上升沿,master驱动地址和控制信号; HCLK下一周期上升沿,slave采样地址和控制信息;

注2:任意一次传输地址阶段,同时是上一次传输的数据阶段(总线地址和数据的交叠是总线流水线pipelined特点的基础);

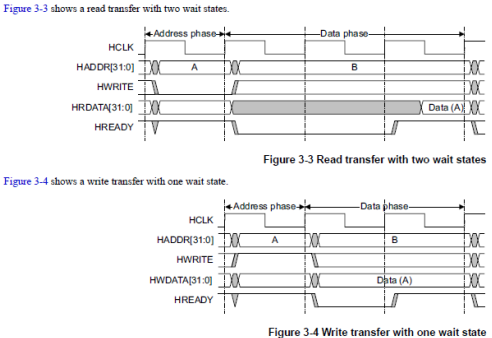

(2)slave插入等待状态的传输;

注1:slave可以插入等待状态以有足够的时间完成传输;

注2:每个slave由HREADYOUT信号,在数据阶段驱动HREADY信号,互连负责将所有slave的HREADYOUT信号组合产生一个HREADY信号来控制整个传输进度;

注3:对于读操作,在等待状态下,slave不需要提供有效数据直至传输快要结束,即在传输的最后一个周期提供即可;

注4:对于写操作,在extended周期中或等待状态下,master需要保持数据稳定不变,参考图3-4;

注5:slave插入等待状态的传输的副作用是会影响到下一次传输的地址阶段,需要延长下一笔传输的地址周期(地址B的读操作过程中,插入了等待状态;这对地址C的操作造成了影响,地址C在地址B操作完成前需要保持不变);

3.2传输类型

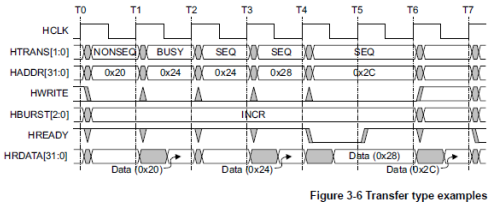

(1) HTRANS=2'b00,空闲状态IDLE,主设备占用总线,但不需要数据传输,也没有进行传输;slave必须提供0等待的OKAY响应,并且master??slave??忽略该传输(两次burst传输中间主设备发IDLE);

(2) HTRANS=2'b01,忙传输BUSY,master可以在突发传输的中间插入空闲周期,表示master继续突发传输,但master还没有准备好下一次传输,下一次传输不能立即发生;这种情况下,突发传输中地址和控制信号必须反映下一次传输,也就是准备下一次传输的地址阶段;仅仅未定义长度的突发传输可以在最后一个周期进行忙传输???; slave必须提供0等待的OKAY响应,并且master??slave??忽略该传输;

(3) HTRANS=2'b10,非连续突发传输NON-SEQ,表明是单次传输或突发传输中的第一个;地址与控制信号和上一次传输没有关联(burst的其他拍是前一次地址的增加); 单次传输视为长度为1的突发传输,因此也视为非连续的;

(4) HTRANS=2'b11,连续突发传输SEQ;突发传输余下的都是连续的,地址和前一次传输有关,控制信号和前一次传输一样,但地址等于前一次传输地址加上传输的大小,传输的大小通过HSIZE信号反映;

注1:在图3-6中,T1-T2内,master无法进行第二拍读,插入BUSY状态来延迟第二拍,而slave则提供第一拍的数据;

注2:T2-T3内,master准备启动第二拍,进入SEQ状态,master忽略slave在读数据总线提供的任何数据;

注3:T3-T4内,master启动第三拍,slave提供第二拍的数据;

注4:T4-T5内,master启动最后一拍,slave不能完成传输,拉低HREADY来插入等待状态; T5-T6, slave提供第三拍的数据; T6-T7, slave提供最后一拍的数据;

浙公网安备 33010602011771号

浙公网安备 33010602011771号