?-sva/system verilog assertion与功能覆盖

参考资料

(1) 请教一下用assert property和cover property搜集覆盖率有什么不同? - IC验证讨论 - EETOP 创芯网论坛 (原名:电子顶级开发网) -

(2) sv绿皮书;

(3) IEEE system verilog standard;

1.功能覆盖与cover

(1) 功能覆盖是按照设计规范衡量验证状态的一个标准,它可以分成两类:协议覆盖和测试计划覆盖.

(2) 断言可以用来获得有关协议覆盖的穷举信息。SVA提供了关键词“cover”来实现这一功能.

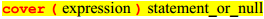

(3) cover语句的基本语法如下所示。

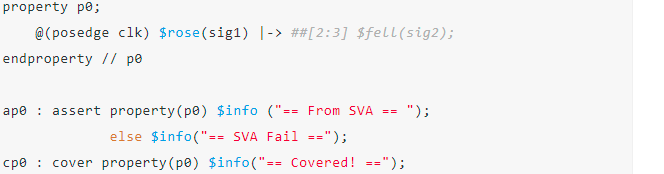

<cover_name> : cover property (property_name)

“cover_name”是用户提供的名称,用来标明覆盖语句,“property_name”是用户想获得覆盖信息的属性名。

(4) cover语句的结果包含信息:属性被尝试检验的次数,属性成功的次数,属性失败的次数,属性空成功的次数。

检验器“mutex_clk”在一次模拟中的覆盖日志的实例如下所示。

![]()

2.cover与assert的异同

(1) 像断言(assert)语句一样,覆盖(cover)语句可以有执行块.在一个覆盖成功匹配时,可以调用一个函数(function)或者任务(task),或者更新一个局部变量。

(2) assert是执行了这段断言并且成功了就会覆盖,否则报错,当需要用断言去验证时序正确性的时候,可以用assert; cover则是执行了这段断言,成功就覆盖,没成功不会报错,当用断言去覆盖时序的异常场景时,可以用cover;

浙公网安备 33010602011771号

浙公网安备 33010602011771号