篇8-sva/system verilog assertion检验器的时序窗口(重叠的时序窗口和无限的时序窗口)

资料来源

例子:

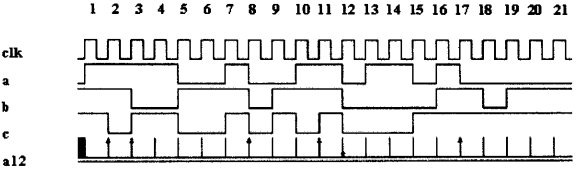

属性p12检查布尔表达式“a&&b”在任何给定的时钟上升沿为真。如果表达式为真,那么在接下来的1~3个中周期内,信号“c”应该至少在一个时钟周期内为高。

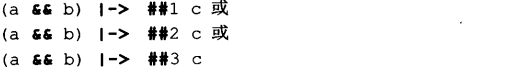

p12实际上以下面三个线程展开。

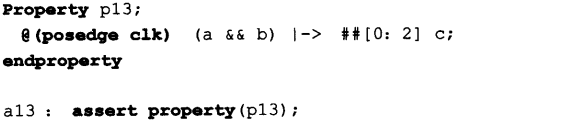

1.重叠的时序窗口

属性p13与属性p12相似。两者最大的区别是p13的后续算子在先行算子成功的同一个时钟沿开始计算。

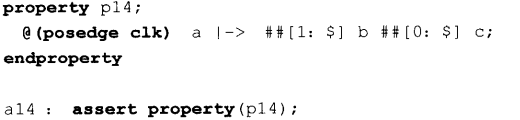

2.无限的时序窗口

(1) 在时序窗口上限可以用“$”定义,这表明时序没有上限。这叫做“可能性”(eventuality)。检验器不停地检查表达式是否成功直到模拟结束。因为会对模拟器的性能产生巨大的负面影响,所有这不是编写SVA的一个高效的方式。最好总是使用有限的时序窗口上限。

浙公网安备 33010602011771号

浙公网安备 33010602011771号