4-sva/system verilog assertion中序列/sequence的构建(1)(包含$rose,$fell,$stable,$changed等函数)

资料来源

(1)硅芯思见:【81】SVA中的$rose和$fell (qq.com)

(2)硅芯思见:【92】SVA中的内嵌函数 (qq.com)

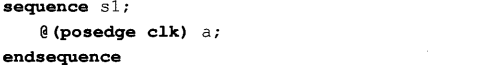

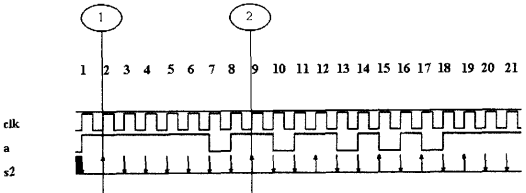

1.简单序列

序列s1检查信号“a”在每个时钟上升沿都为高电平。如果信号“a”在任何一个时钟上升沿不为高电平,断言将失败。

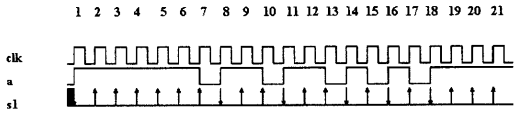

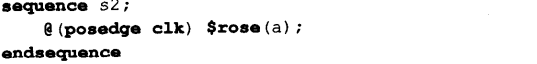

2.边沿定义的序列以及使用其他内嵌函数的序列

2.1边沿定义的序列

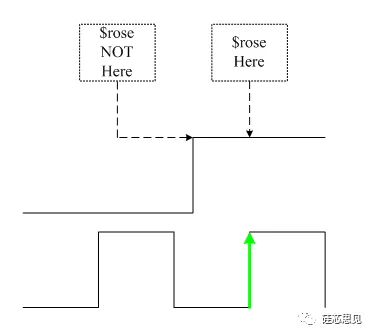

序列s2检查信号“a”在每一个时钟上升沿都跳变成1。如果跳变没有发生,断言失败。

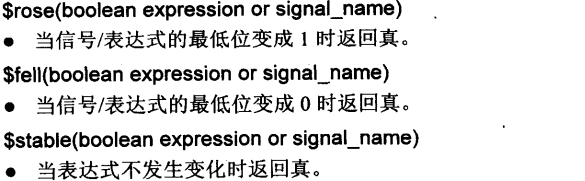

注1:$rose是用于判断时钟采样信号前后是否存在0-1或x-1或z->1的变化; $rose仅对表达式最低位的跳变变化敏感,对于非最低位信号的变化不敏感;

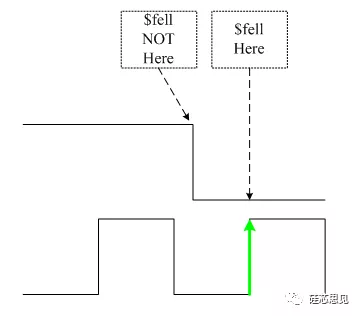

注2:$fell用于判断时钟采样信号前后是否存在1->0或x->0或z->0的变化;

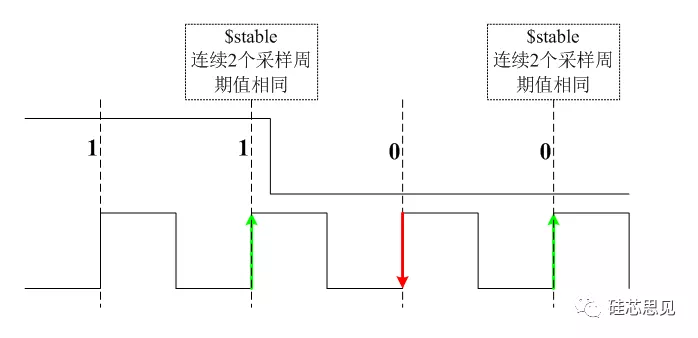

注4:$stable用于判断信号在连续两个采样时钟周期内是否保持不变;

2.2使用其他内嵌函数的序列($onehot, $onehot0, $isunknown, $countones)

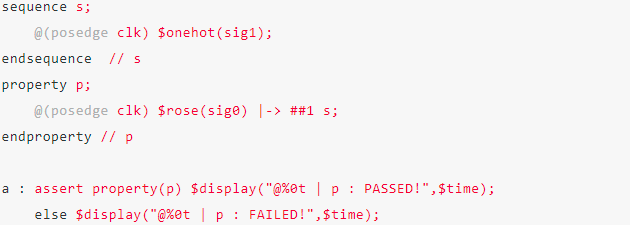

(1) $onehot(expression)

注1:只要表达式最终结果中有且仅有一位为高,该函数即返回真,其他位可以是不定态或高阻态;

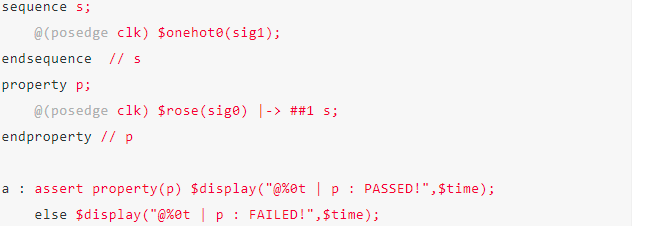

(2) $onehot0(expression)

注1:只要表达式最终结果中有且仅有一位为高或者没有任何一位为高,该函数即返回真,其他位可以是不定态或高阻态;

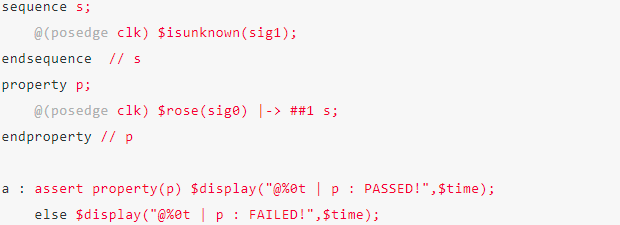

(3) $isunknown(expression)

注1:该函数用于检验表达式最终结果中的各位中是否有x或者z;如果存在x或z,$isunknown就会返回真,如果不存在,$isunknown就会返回假;

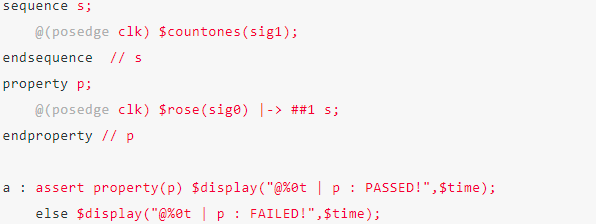

(4) $countones(expression)

注1:用于获取表达式最终结果中电平为高的位的个数;如果表达式中没有任何一位为高电平,则$countones返回为0,如果有一位或多位为高,$countones返回为不为0的位的个数;

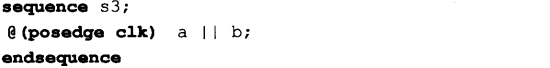

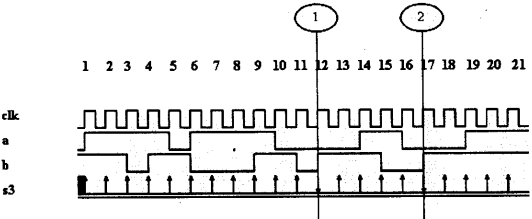

3.逻辑关系的序列

序列s3检查每一个时钟上升沿,信号“a”或者信号“b”是高电平,则断言成功。如果两个信号都是低电平,断言失败。

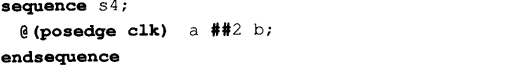

4.时序关系的序列

序列s4检查信号“a”在一个给定的时钟上升沿为高电平,如果信号“a”不是高电平,序列失败。如果信号“a”在任何一个给定的时钟上升沿为高电平,信号“b”应该在两个时钟周期后为高电平。如果信号“b” 在两个时钟周期后不为1,断言失败。注意,序列以信号“a”在时钟上升沿为高电平开始。

浙公网安备 33010602011771号

浙公网安备 33010602011771号