2-【IMP】assertion的作用,特点与分类

资料来源

1.什么是断言?

断言是设计的属性的描述;

如果一个在模拟中被检查的属性不像我们期望的那样表现,那么这个断言失败;

如果一个被禁止在设计中出现的属性在模拟过程中发生,那么这个断言失败;

2.为什么使用断言?

(1) verilog是一种过程语言,不能很好地控制时序; verilog语言的过程性这一本质使得测试同一时间段内发生的并行时间比较困难; verilog语言没有提供内嵌的机制来提供功能覆盖的数据,用户需要自己实现该部分代码;

(2) sva是一种描述性语言,可以完美地描述时序相关的状况;此外,sva提供若干内嵌函数来测试特定的设计情况,并且提供一些构造来自动收集功能覆盖数据;

3.断言的特点

(1) 使用断言可以缩短研制周期;

(2) 使用断言可以使设计中存在的各种问题更容易被动态监测观察;

(3) 使用断言内嵌的覆盖率统计功能(cover)可以更加容易的获得对于功能的覆盖性;

(4) 断言不止可以用于单一时钟域的设计中,也可以用于多时钟域的设计中;

(5) 断言的可读性较一般描述语言更容易理解;

(6) 断言可以形成AIP(assertion ip),复用于其他项目;

(7) 通过全局控制实现设计中断言的开关;

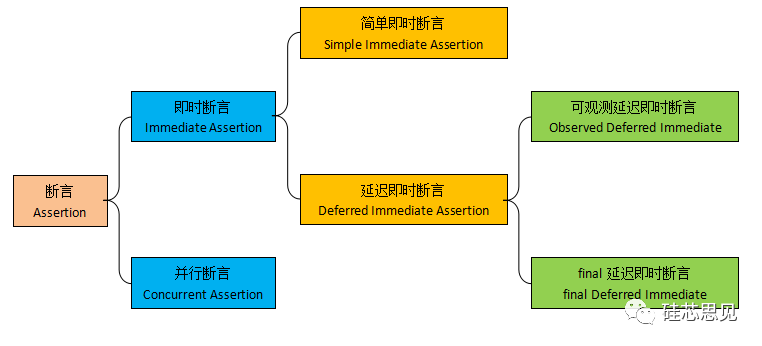

4.断言的分类

4.1 并发断言

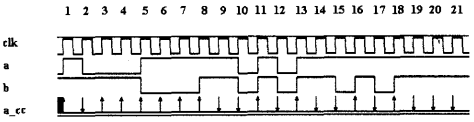

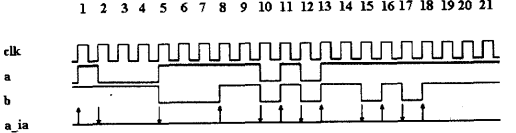

(1) 基于时钟周期(属性在每一个时钟的上升沿被检验)。

(2) 在时钟边缘根调用的变量的采样值计算测试表达式。

(3) 变量的采样在预备阶段完后,而表达式的计算在调度器的观察阶段完成。

(4) 可以被放到过程块(procedural block)、模块(module)、接口(interface),或者一个程序(program)的定义中。------并行断言的位置

(5) 可以在静态(形式的)验证和动态验证(模拟)工具中使用。

![]()

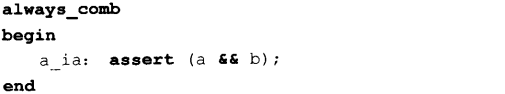

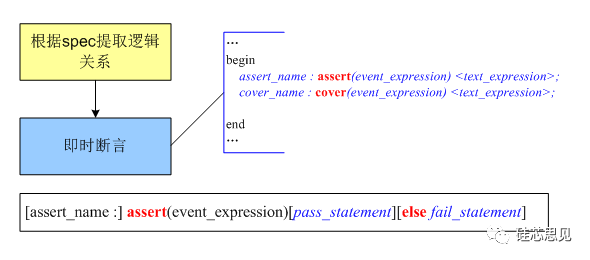

4.2 即时断言

(1) 基于模拟事件的语言(当信号发生变化时,执行检测),其行为一般不依赖于具体时钟。

(2) 测试表达式的求值就像在过程块中的其他Verilog的表达式一样。它们的本质不是时序相关的,而且立即被求值。

(3) 必须放在过程块的定义中。------即时断言的位置

4.3 并行断言与即时断言形式上的差异

(1) 关键词property;

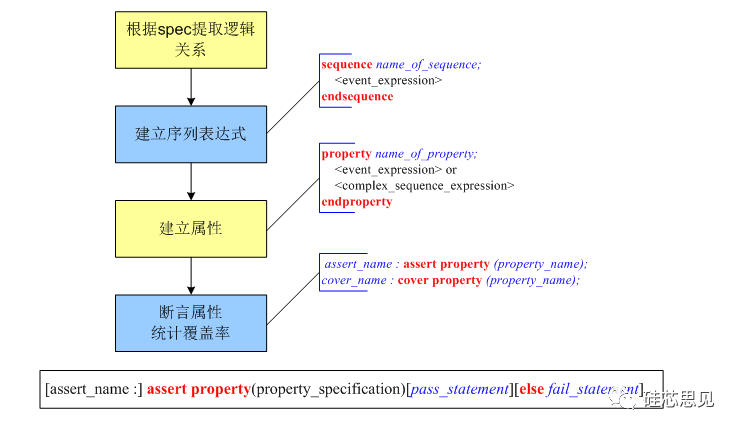

5.断言的添加

(1) 一般情况下,不论是设计人员还是验证人员,在构建各自的设计时都需要增加嵌入一定的断言。

(2) 对于设计人员来说,设计人员对于芯片的内部结构和逻辑更加了解,所以设计人员更适合在设计中插入断言。

(3) 对于验证人员来说,验证人员因为需要访问芯片的各种接口,需要构建各种不同的测试用例,施加不同的激励,更适合在接口增加断言,实现对于接口和宏观功能的检查。

(4) 一般在一个电路的设计验证过程中可以在以下部位考虑增加断言设计:

Ø 模块内部的断言,例如设计中的状态机的状态跳转、特定的编码结构、存储器等;

Ø 模块间的接口时序,特别是具有特定协议要求的接口;

Ø 芯片端口的时序和具有特定的协议要求的接口;

Ø 功能性测试,特定的协议握手等;

Ø 对于设计中不期望的部分,可以使用断言用以提示此处代码不期望被测试等;

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· .NET Core 中如何实现缓存的预热?

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· Linux系列:如何用heaptrack跟踪.NET程序的非托管内存泄露

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· Manus的开源复刻OpenManus初探

· 三行代码完成国际化适配,妙~啊~

· .NET Core 中如何实现缓存的预热?

· 阿里巴巴 QwQ-32B真的超越了 DeepSeek R-1吗?