篇5-testcase pass的判断

资料来源:

(1) 公众号-杰瑞IC验证

1.统计UVM_FATAL与UVM_ERROR数目

(1) 在uvm_test或env的final_phase里面,检查UVM_ERROR和UVM_FATAL的个数,如果不为0,打印CASE FAIL;否则,打印CASE PASS;

(2) 示例中,之所以采用$display,而不是uvm_fatal和uvm_info,是因为二者可能会被屏蔽掉(比如冗余度的改变),会影响后期检索;

(3) 之所以不直接排查仿真log里的UVM_ERROR和UVM_FATAL,是因为仿真可能在没有uvm_error和uvm_fatal的情况下异常结束,比如超时或磁盘满了,或者提交到服务器的任务被管理员kill等;

2.注意排查SVA assertion错误

(1) SVA assertion错误的格式是***Offending***;

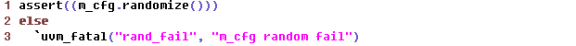

3.注意排查随机约束错误

(1) 有些仿真器并不会因为随机失败而提前结束仿真;对于显式的随机约束,最好在randomize前加上assert,并提供合适的display信息;

(2) 对于`uvm_do_with, `uvm_rand_send等内嵌的隐式随机约束,不能直接加assert,需要在仿真log内对随机约束失败进行排查(这种情况下,错误格式会因仿真工具而异);

4.排查参考模型错误

(1) 参考模型里面的打印信息可能没有记录到仿真log里,需要在调用参考模型时,将打印信息记录到log中,并对log检查;

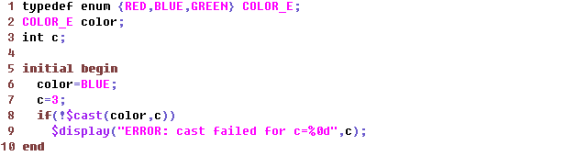

5.排查类型转换错误

(1) 常见问题是将int变量直接复制给一个枚举变量,类型转换失败;

(2) 解决办法:对不同类型赋值时,尽量使用$cast转换;

6.预防DUT空转

(1) 检查激励有效性;

(2) 对monitor和scoreboard内的关键信号或数据检查进行计数,在final_phase里判断这些计数器是否为0;

浙公网安备 33010602011771号

浙公网安备 33010602011771号