篇1-sv/uvm命令行参数

参考资料:

(1) 公众号-芯片学堂;

(2) uvm中获取cmdlind内容 | 骏的世界 (lujun.org.cn)

背景:当在创建动态仿真case时,使用命令行参数可以方便地控制DUT和TB的行为,比如配置寄存器、控制激励的发送数量、打开或关闭某些scoreboard等;

1.sv系统函数($test$plusargs(arg_string)与$value$plusargs(arg_string, target_var))

(1) 通过命令行来传递参数在实际项目中算是常规操作,比如通过命令行参数来指定Testbench的配置信息等等。

(2) 在SystemVerilog LRM规范里,命令行提供的仿真参数要求使用加号(+)作为引导,这部分参数可以被验证环境中的SV代码通过系统函数访问到。由于是额外增加的,这些参数也就被称之为plusargs。

(3) 访问plugargs的系统函数有$test$plusargs(arg_string)和$value$plusargs(arg_string, target_var)。这两个系统函数都会根据用户指定的字符串arg_string,去检索plusargs列表。如果找到了,则系统函数返回值1;如果没有找到,返回值0。

1.1$test$plusargs(arg_string)

$test$plusargs(arg_string)可以被用于判断命令行是否带了arg_string参数,以此来作为验证环境的配置开关;

1.2$value$plusargs(arg_string, target_var)

$value$plusargs(arg_string, target_var)是在$test$plusargs的基础上,增加了对参数arg_string的值的解析:如果匹配到了arg_string,系统函数会将其值赋给target_var;如果没有找到,则不修改target_var的值。

2.sv系统函数($test$plusargs(arg_string)与$value$plusargs(arg_string, target_var))的缺点

(1) 位置太随意,可以在module, class, interface等任何能使用begin/end块的地方解析命令行参数,这样会造成互相影响;

(2) 命令行参数的格式必须同解析的格式一样,否则会传递失败,甚至传递错误的值;比如,按照16进制解析的参数,如果按照10进制传递,就会传递错误的值;

(3) 不支持数组和枚举类型的数据;

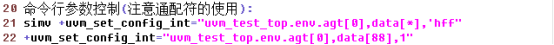

3.uvm_cmdline_processor(提供当前仿真命令行参数的接口)

(1) uvm定义的一套命令行参数规则,可以方便地从命令行传递常用类型数据到tb里;

(2) uvm_cmdline_processor继承自uvm_report_object,再往上到uvm_object。

(3) uvm_cmdline_processor提供的底层函数接口,跟$test$plusargs和$value$plusargs没有什么大的区别,不过其中有匹配功能或返回参数列表的函数,对于uvm_root解析UVM配置相关的参数很有帮助。

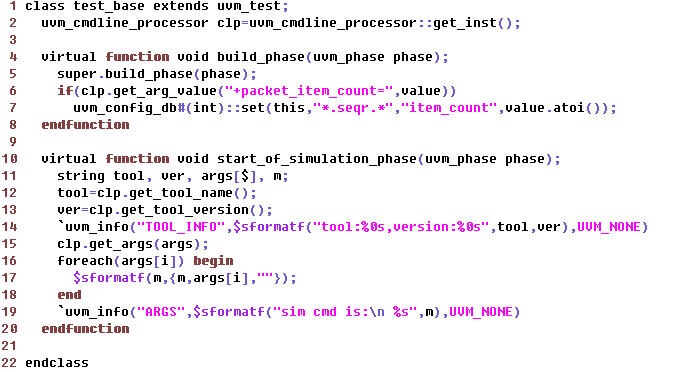

(4) uvm_cmdline_processor是单实例类,并提供了get_inst()静态方法用来获取对象句柄。UVM默认在初始化的时候,会构造uvm_cmdline_processor的全局对象,叫uvm_cmdline_proc。在实际使用中,按照习惯,先声明一个uvm_cmdline_processor句柄,然后通过get_inst()函数来指向uvm_cmdline_processor对象。

(5) uvm命令行参数什么时候生效:new函数之后,build_phase的super.build_phase中;

(6) uvm命令行参数的限制:uvm命令行参数目前只能给component传递,不能给object传递;

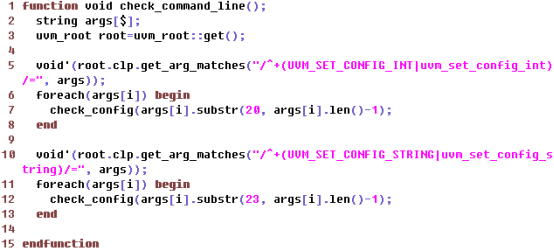

3.1 function get_arg_matches

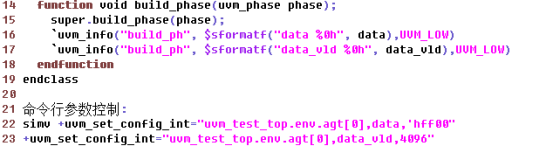

4.uvm_cmdline_processor使用示例

4.1 传递int类型参数

4.2 传递string类型参数

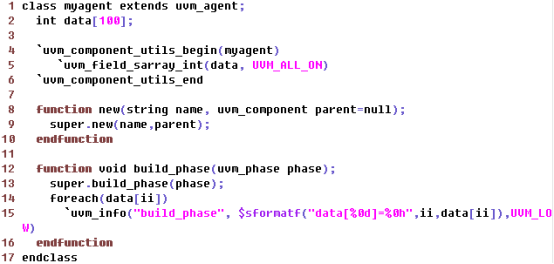

4.3 传递int数组参数

浙公网安备 33010602011771号

浙公网安备 33010602011771号