篇1-interface

资料来源:

(1)公众号-芯片学堂;

(2)The UVM Primer;

1.接口的作用与构成

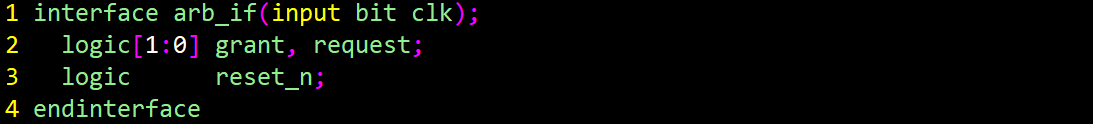

(1)接口将一组信号封装到一起,方便信号在验证环境组件中的连接;

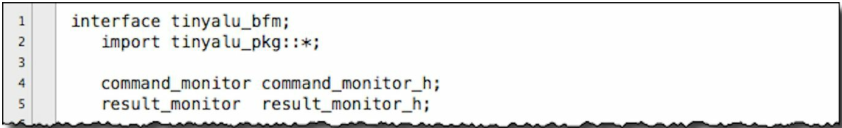

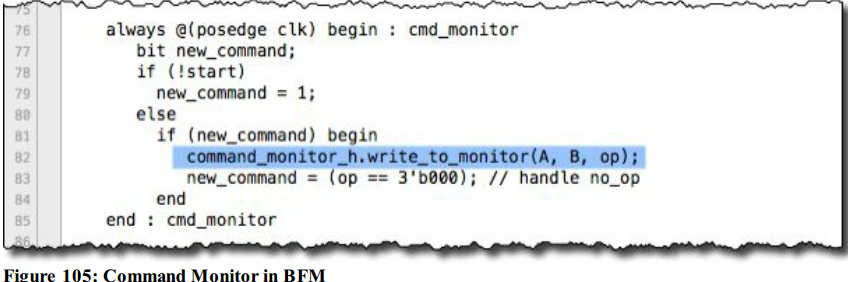

(2)接口不只包含一组信号,还可以包含modport,clocking block,parameter,always和initial语句块,assign语句,断言assertion,覆盖组,函数和任务,事件event等(复杂使用)(这些特点使得接口可以用于构建Bus Functional Model,将和总线协议相关的内容通过interface中的子程序实现);

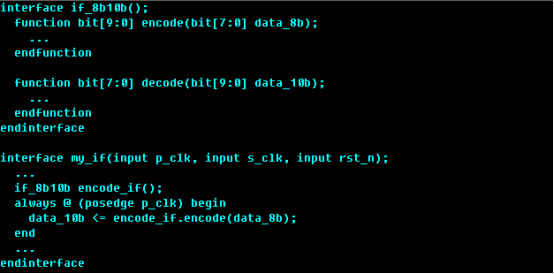

(3)接口内可以实例化其他接口;

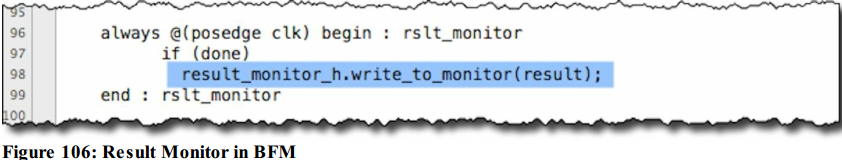

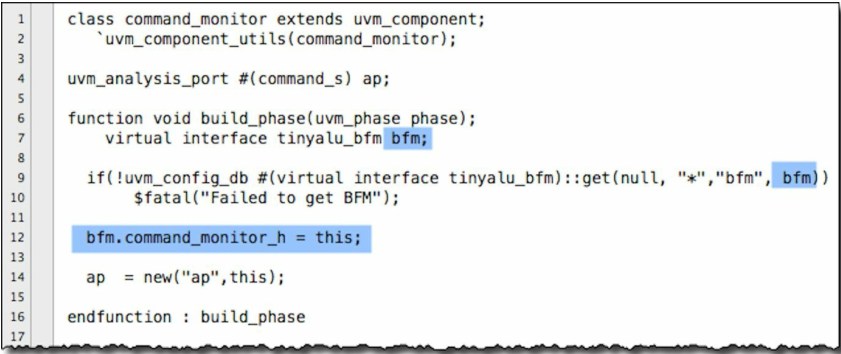

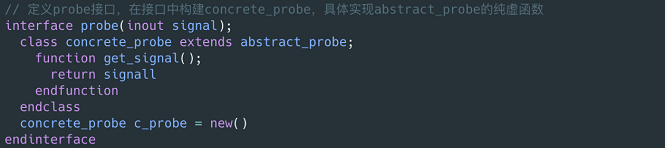

(4)接口内可以使用类的句柄(如下图所示, command_monitor与result_monitor这两个类的定义位于tinyalu_pkg内;在uvc的build_phase内为interface中的句柄赋值);

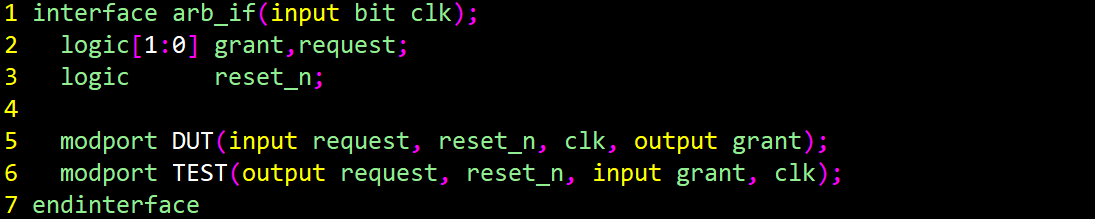

1.1modport

(1)modport可以用来在接口中定义信号的方向(这种方向的定义相当于对信号施加了连接约束,避免在模块或环境组件集成的过程中连接出错);

(2)一个interface中可以提供任意数量的modport;

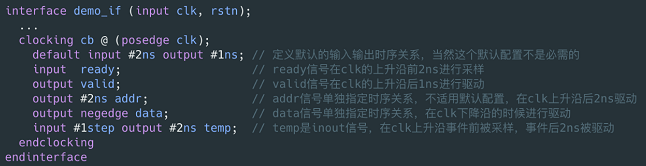

1.2clocking block(控制同步信号)

(1)时钟块中,可以清楚定义各个信号相对于时钟边沿的时序关系,确定信号被驱动或采样的时刻;

(2)采样输入信号(input),驱动输出信号(output);

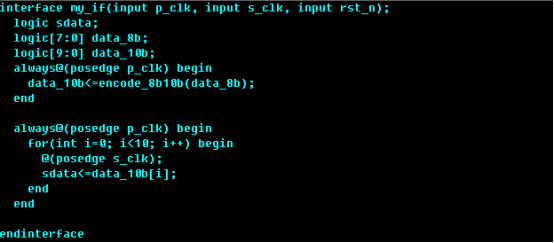

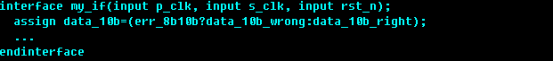

1.3 always语句块 & assign语句

1.4 interface内例化interface

注:该示例中,interface if_8b10b与DUT根本没有任何接触,只是为了提高代码的可重用性,单纯起到一个封装的作用.

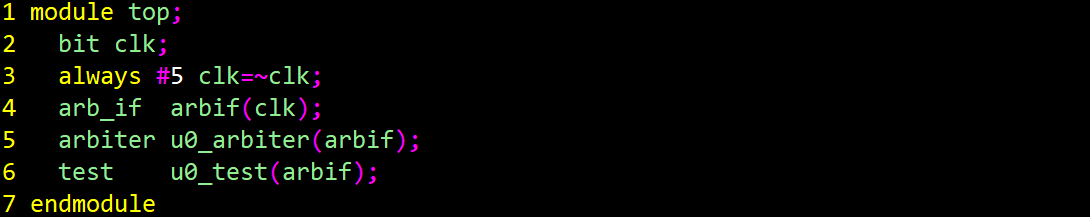

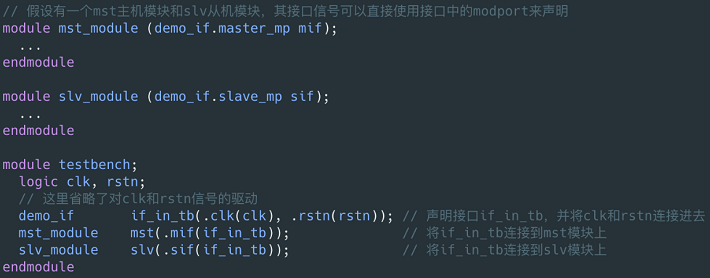

2.interface的集成

2.1static pin to pin

(1)在顶层模块中声明所有信号或者接口,然后分别在例化子模块时,完成连接;

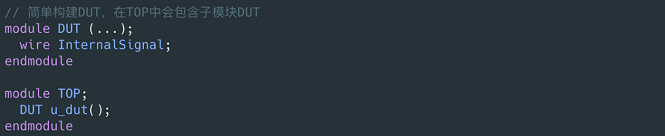

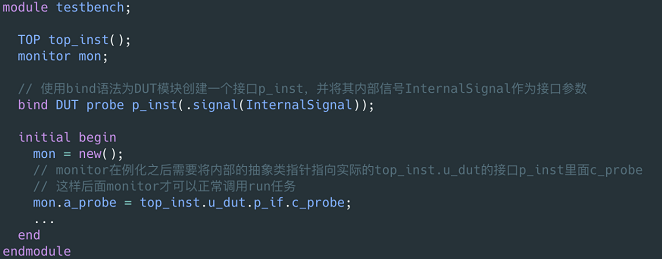

2.2 bind

浙公网安备 33010602011771号

浙公网安备 33010602011771号