[CU]reg model使用篇-reg model使用示例之uvc/seq内使用reg model

参考资料:

(1) 《Practical UVM step by step with IEEE》

(2) 《UVM实战-张强》

1. uvc内使用regmodel

1 //示例1:reference model中使用reg model; 2 class my_model extends uvm_component; 3 ... 4 reg_model p_rm; 5 ... 6 endclass 7 8 task my_model::main_phase(uvm_phase phase); 9 my_transaction tr; 10 my_transaction new_tr; 11 12 uvm_status_e status; 13 uvm_reg_data_t value; 14 super.main_phase(phase); 15 p_rm.invert.read(status,value,UVM_FRONTDOOR); 16 17 while(1) begin 18 port.get(tr); 19 new_tr=new("new_tr"); 20 new_tr.copy(tr); 21 if(value) invert_tr(new_tr); 22 ap.write(new_tr); 23 end 24 25 endtask 26 27 function void my_env::connect_phase(uvm_phase phase); 28 ... 29 mdl.p_rm=this.p_rm; 30 ... 31 endfunction

1 //示例2:test中使用reg_model; 2 class vga_lcd_reg_single_access_test_frontdoor extends vga_lcd_env_base_test; 3 `uvm_component_utils(vga_lcd_reg_single_access_test_frontdoor) 4 5 ral_block_vga_lcd ral_regmodel; 6 uvm_status_e status; 7 uvm_reg_data_t value_w; 8 uvm_reg_data_t value_r; 9 uvm_reg rg; 10 11 function new(string name, uvm_component parent); 12 super.new(name,parent); 13 endfunction 14 15 task main_phase(uvm_phase phase); 16 uvm_objection phase_done=phase.get_objection(); 17 phase_done.raise_objection(this); 18 value_w=32'h0000_1111; 19 20 rg=env.ral_regmodel.HTIM; 21 `uvm_info(get_full_name(),"Starting Backdoor write access to HTIM", UVM_LOW) 22 rg.write(status,value_w,.path(UVM_BACKDOOR)); 23 `uvm_info(get_full_name(),"Ending Backdoor write access to HTIM", UVM_LOW) 24 25 `uvm_info(get_full_name(),"Starting Backdoor read access to HTIM", UVM_LOW) 26 rg.read(status,value_r,.path(UVM_BACKDOOR)); 27 `uvm_info(get_full_name(),"Ending Backdoor read access to HTIM", UVM_LOW) 28 29 env.ral_regmodel.HTIM.write(status,value_w,.path(UVM_BACKDOOR)); 30 env.ral_regmodel.HTIM.read(status,value_r,.path(UVM_BACKDOOR)); 31 32 phase_done.set_drain_time(this,200); 33 phase_done.drop_objection(this); 34 endtask 35 36 endclass

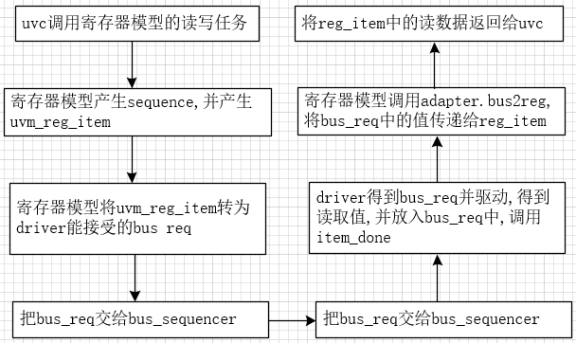

1.1 uvc内使用reg model具体操作过程(初级版本-注意resp的处理)

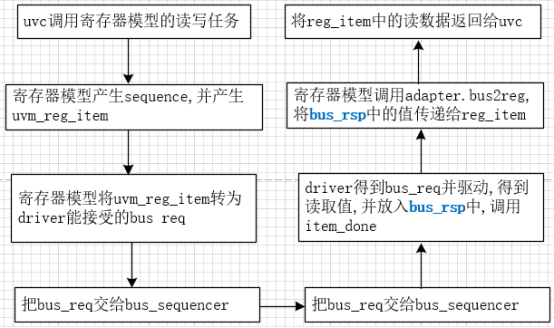

1.2 uvc内使用reg model具体操作过程(通用版本-注意resp的处理)

2. sequence内使用寄存器模型

(1) 先在对应的sequencer中定义一个顶层reg_block指针,并指向base_test的reg_block对象;

(2) 在sequence中调用p_sequencer进行访问;

1 class case0_cfg_vseq extends uvm_sequence; 2 ... 3 virtual task body(); 4 uvm_status_e status 5 uvm_reg_data_t value; 6 p_sequencer.p_rm.invert.write(status,1,UVM_FRONTDOOR); 7 endtask 8 ... 9 endclass

浙公网安备 33010602011771号

浙公网安备 33010602011771号