[CU]reg model使用篇-reg model使用示例之将reg model添加到base_test或env中【在更高的层次谈reg model】

前言

(1) 该篇文章的前提: (a) register model已经创建; (b) register adapter已经创建;

(2) 该篇文章的主要内容: (a) 在顶层env中,实例化register model; (b) 锁定register model,不允许进一步的变动; (c) 建立register model与register adapter的联系;

1. regmodel与其他验证组件的关系与交互

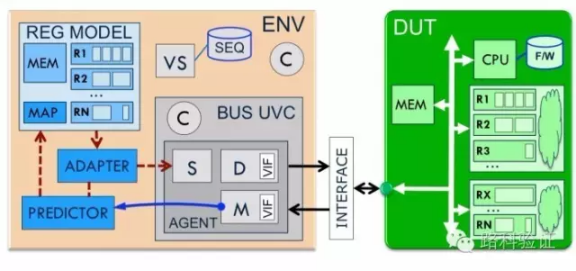

(1) 在验证环境中,顶层的寄存器模块与其他验证组件并行初始化,如下图所示.

(2) 整个验证平台只创建一个reg model对象,在其他地方使用指针调用; 一般在test中例化顶层reg_block, adapter与predictor;

(3) 寄存器模型和验证环境中其余组件的信息交互主要通过adapter和predictor这两个组件完成.

注1: uvm_reg_adapter:用于实现uvm_reg_item与bus_trans的转换(与前门访问相关);

注2: uvm_reg_predictor: 基于monitor观测到的transactions更新寄存器模型,用于显式预测(与前门访问相关).

2. 将reg model添加到base_test或env中

(1) 定义reg_model(reg_block)与reg_sqr_adapter(reg_adapter);

(2) build_phase内,实例化reg_model;

(3) build_phase内,调用reg_model的configure函数,把reg_model的绝对路径加进去,该路径和reg_model中寄存器的路径组合起来实现相关寄存器的BACKDOOR操作.

1 reg_model.configure(null, "top_tb.dut_inst");

(4) build_phase内,调用reg_model的build函数,将所有uvm_reg实例化;

(5) build_phase内,调用reg_model的lock_model与reset函数.

注1: 调用lock函数后,reg_model中不能加入新的寄存器;

注2: 调用reset函数后,所有寄存器的值都将变为设置的复位值;

(6) connect phase内,调用address_map(default_map或者用户自定义的address_map)的set_sequencer方法,并把前门操作的bus sequencer和adapter作为参数传入;

(7) connect_phase内,实现predictor analysis_imp与bus_monitor的analysis port的连接(上文没有描述predictor的定义??predictor不需要额外定义,可以直接使用uvm库中参数化的类);

1 class base_test extends uvm_test; 2 my_env env; 3 my_vsqr vsqr; 4 reg_model rm; 5 my_adapter reg_sqr_adapter; 6 ... 7 endclass 8 9 function void base_test::build_phase(uvm_phase phase); 10 super.build_phase(phase); 11 env =my_env::type_id::create("env",this); 12 vsqr=my_env::type_id::create("vsqr",this); 13 14 rm=reg_model::type_id::create("rm",this); 15 rm.configure(null,""); 16 rm.build(); 17 rm.lock_model(); 18 rm.reset(); 19 20 reg_sqr_adapter=new("reg_sqr_adapter"); 21 env.p_rm=this.rm; 22 23 endfunction

2.1 connect_phase采用auto_predict预测方法

1 function void base_test::connect_phase(uvm_phase phase); 2 ... 3 vsqr.p_rm=this.rm; 4 rm.default_map.set_sequencer(env.bus_agt.sqr, reg_sqr_adapter); 5 rm.default_map.set_auto_predict(1); 6 endfunction

2.2 connect_phase采用显式预测方法(使用uvm_predictor)

1 virtual function void connect_phase(uvm_phase phase); 2 super.connect_phase(phase); 3 reg_block.default_map.set_sequencer(apb_agent.sequencer, adapter); 4 5 predictor.map=reg_block.default_map; 6 predictor.adapter=adapter; 7 apb_agent.monitor.output_port.connect(predictor.bus_in); 8 9 endfunction

3. 使用示例

(1)示例一: UVM学习笔记--寄存器模型 Register Model_wonder_coole的博客-CSDN博客_寄存器模型

1 class simple_ral_env extends uvm_env; 2 ral_block_simple_ral_env regmodel; 3 wb_master_agent master_agent; 4 5 wb_ral_reg_adapter reg2host; 6 uvm_reg_predictor #(wb_transaction) wishbone_reg_predictor; 7 8 `uvm_component_utils(simple_ral_env) 9 10 extern function new(string name="simple_ral_env", uvm_component parent=null); 11 extern virtual function void build_phase(uvm_phase phase); 12 extern virtual function void connect_phase(uvm_phase phase); 13 14 endclass: simple_ral_env 15 16 function simple_ral_env::new(string name= "simple_ral_env",uvm_component parent=null); 17 super.new(name,parent); 18 endfunction:new 19 20 function void simple_ral_env::build_phase(uvm_phase phase); 21 super.build_phase(phase); 22 master_agent = wb_master_agent::type_id::create("master_agent",this); 23 24 this.regmodel = ral_block_simple_ral_env::type_id::create("regmodel",this); 25 regmodel.build(); 26 regmodel.print(); 27 reg2host = new("reg2host"); 28 regmodel.add_hdl_path("simple_ral_env_top.dut","RTL"); 29 wishbone_reg_predictor = uvm_reg_predictor #(wb_transaction)::type_id::create("wishbone_reg_predictor",this); 30 regmodel.lock_model(); 31 endfunction: build_phase 32 33 function void simple_ral_env::connect_phase(uvm_phase phase); 34 super.connect_phase(phase); 35 regmodel.default_map.set_sequencer(master_agent.mast_sqr,reg2host); 36 wishbone_reg_predictor.map = regmodel.default_map; 37 wishbone_reg_predictor.adapter = reg2host; 38 master_agent.mast_mon.mon_analysis_port.connect(wishbone_reg_predictor.bus_in); 39 40 endfunction: connect_phase

浙公网安备 33010602011771号

浙公网安备 33010602011771号