Modelsim LPM(fifo, PLL)仿真关注

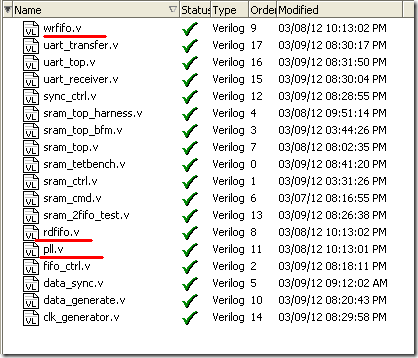

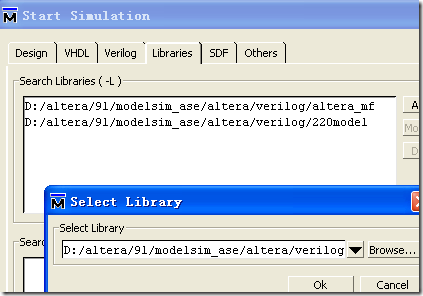

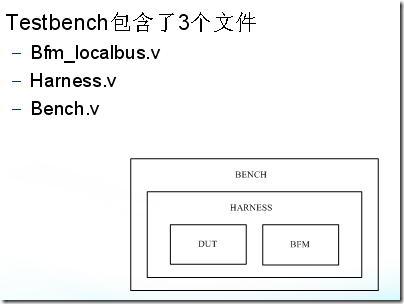

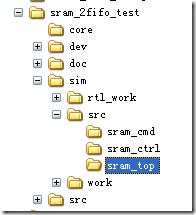

在用第三方软件:Modelsim对Quartus II LPM进行仿真的时候,要加入例化生成的.v文件,以及在simulation的时候加入altera的库,如下:

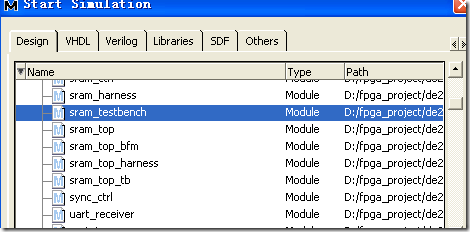

(顺便说一句,Modelsim中testbench顶层文件只能有一个。。。。书上都没说的。。)

LPM – PLL 注意:

今天在用Modelsim做一个后仿真的时候,发现PLL的没有输出,在设定不同的测试时钟频率的时候,出现一下三种情况:

(1)当输入时钟周期小于在例化PLL时选择的输入时钟周期时,在运行仿真时,会出现以下警告信息:

Warning : Input clock freq. is under VCO range. Cyclone III PLL may lose lock

(2)当输入时钟周期大于在例化PLL时选择的输入时钟周期时,在运行仿真时,会出现以下警告信息:

Warning : Input clock freq. is over VCO range. Cyclone III PLL may lose lock

这上面这两种情况下,PLL都不会正常工作。如果出现上面第一种情况,可以将输入测试时钟的周期设置大一些。如果出现第二种情况,可以将输入测试时钟的周期设置小一些。

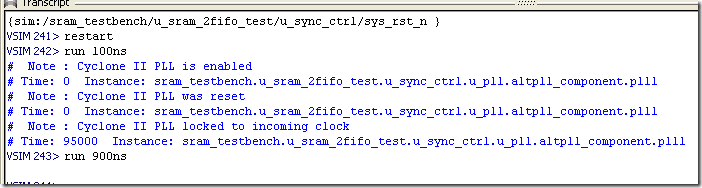

(3)当输入时钟周期等于在例化PLL时选择的输入时钟周期时,在运行仿真时,会出现以下信息:

Note : Cyclone III PLL locked to incoming clock

这有这种情况下PLL才能正常工作!正常工作note如下

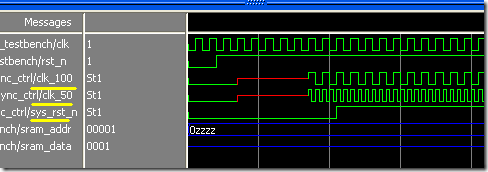

波形仿真如下:

顺便晒晒modelsim的艺术:

posted on 2012-03-09 21:03 CrazyBingo 阅读(1938) 评论(0) 编辑 收藏 举报