Quartus II+Modelsim各种仿真验证

Quartus II+Modelsim各种仿真验证

CrazyBingo

2012-3-2

参考无双oo前辈的博文:

http://www.cnblogs.com/oomusou/archive/2009/01/30/modelsim_pre_post_simulate.html

参考book:《Altera FPGA/CPLD设计 初级篇》第二版

一、FPGA的设计验证流程

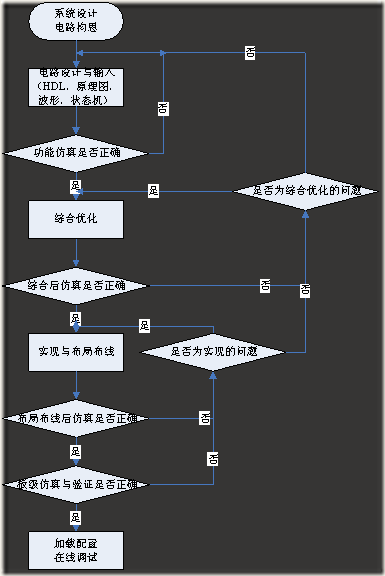

图1:FPGA/CPLD设计完整流程

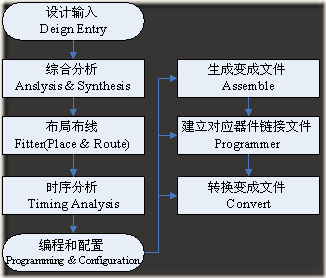

图2:FPGA/CPLD设计简要流程

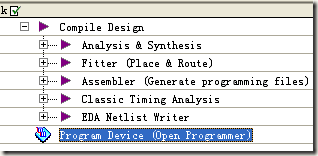

图3:Quartus II中编译步步为营

二、仿真步骤各种概念与步骤

1) 前仿真

前仿真,即功能仿真,用专用放着工具对设计进行功能仿真,验证电路功能是否符合设计要求。通过功能仿真能即使发现设计中的错误,加快设计进度,提高设计的可靠性。

2) 综合后的仿真

把综合生成的标准延时反标注到综合仿真模型去,可估计门延时带来的影响,但是只能估计门延时,不能估计线延时,仿真结果和部先后的实际情况还有一定的差距,并不十分准确。

由于目前综合工具比较成熟,一般省去此环节的仿真。而且在Quartus II中,直接进行下一步仿真。

3) 布局布线后的仿真

即时序仿真。布局布线后生成的仿真延时文件最全,不仅包括门延时,还包括布线延时,所以最为准确,能较好的反映芯片的实际工作情况。

一般来说,布局布线必须进行,以此确保设计的可靠性和稳定性,发现时序违规(Timing Violation)。

4) 板级仿真

在有些高速设计的情况下,还需要使用第三方板级验证工具进行仿真与测试,入MentorTau、Forte Design-Timing Designer、Mentor Hyperlynx、Mentor ICX、Cadence SPECCTRAQuest、Synopsys HSPICE。这些工具通过设计的IBIS和HSPICE等模型的仿真,能较好的分析高速设计信号的完整性、电磁干扰(EMI)等电路特性。

5) 在线仿真

在加载配置目标板之后,设计者在必要情况下要进行的一个步骤,就是在线仿真调试,利用Quartus II自带SignalTap II在线逻辑分析仪进行分析,通过JTAG口,在线、实时读取FPGA内部信号。

一般在我们的设计中但是在我们小型设计中,时序要求不是很严格的情况下,可以省略时序仿真,只进行功能仿真(综合后的仿真一般只在IC设计中用到,一般软件能胜任综合工作,全程编译直接综合→布局布线);大型设计或时序非常严谨的情况下,务必进行时序仿真,验证时序是否违规,进而用timequest进行约束(可以用Quartus II内嵌的静态时序分析(STA),或者第三方(Synopsys的Fprmality、PrimeTime),也可以用Quartus II内嵌的Chip Editor分析芯片内部的连接于配置情况。)。另外在高速电路设计时,为了保证设计的可靠性,务必在时序仿真之后,还要进行一些板级验证。

三、Quartus II 进行功能&时序仿真

(一)Quartus II仿真相关

就算不用第三方软件,Quartus II自个儿也能完成功能仿真和时序仿真,只是波形仿真器不适合庞大的时序,gui做的比较戳罢了。

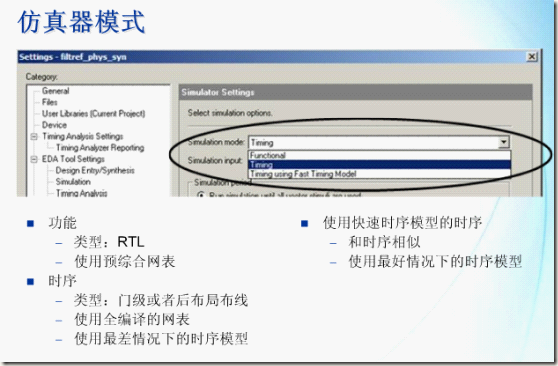

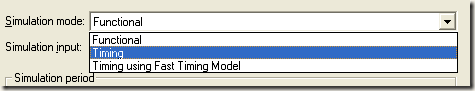

在Quartus II两种仿真,软件分为“function”与“timing”,还有快速时序仿真模型,即功能仿真与时序仿真,可在Device中的Simulator Setting时钟设置。一般我们直接进行或者软件默认为Timing时序仿真。

(二)功能仿真

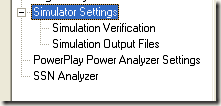

(1)在Setting中设置Simulator为Functional功能仿真

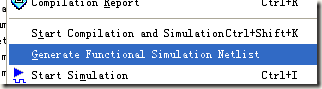

(2)生成功能仿真网标文件

(3)输入激励后进行功能仿真,如下图所示:

(三)时序仿真

(1)在Simulation Setting中选择Timing时序仿真

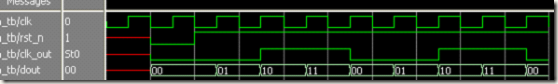

(2)Start simulation,如下图,可以看到时序延时(门级延时与布线延时)

四、Q2+Modelsim进行功能&时序仿真

(一)Modelsim仿真相关

Modelsim是业界最优秀的HDL语言仿真器,但是更专业更牛逼,对于庞大的工程,复杂的时序,如果想Quartus II那样输入激励,坐等蛋碎吧……

相对于Quartus II而言,Modelsim也有功能仿真与时序仿真,只不过功能仿真可以自给自足,而时序仿真需要Quartus II 综合后的网标文件.vo才能进行。

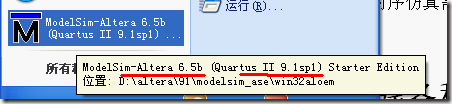

Altera为了用户方便,直接发布了altera版的modelsim,当然必须对应版本才能进行自动仿真。

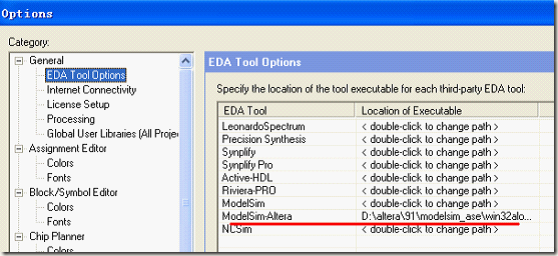

在满足软件版本要求的同时,需要在Quartus II Tool→Option中设置第三方软件路径,如下所述:

对于小白(我是小白)而言,modelsim可以通过在Quartus II的设置自动运行,进行时序仿真或者功能仿真。不过Altera软件中称为RTL级仿真与Gate Level门级仿真,分别对应功能仿真、时序仿真。

(二)功能仿真

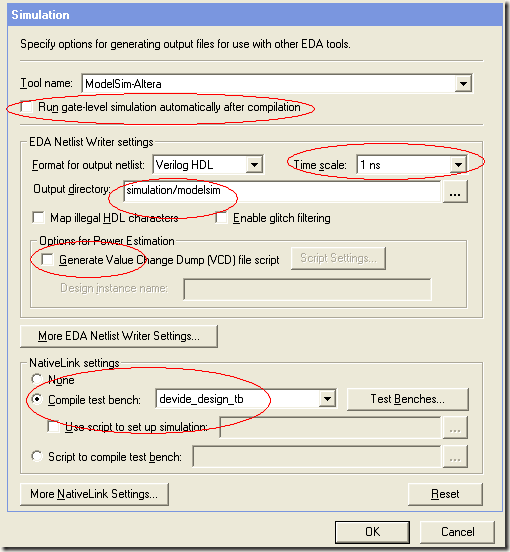

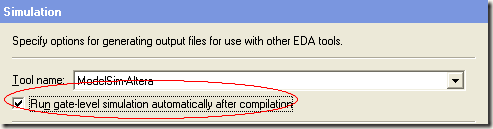

(1)在Quartus EDA Tool Setting→Simulate中设置

如下图,在功能仿真的时候,不用选择在编译后进行门级(时序仿真)

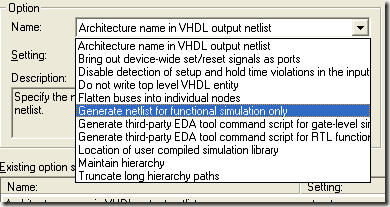

(2)设置自动生成功能仿真网标

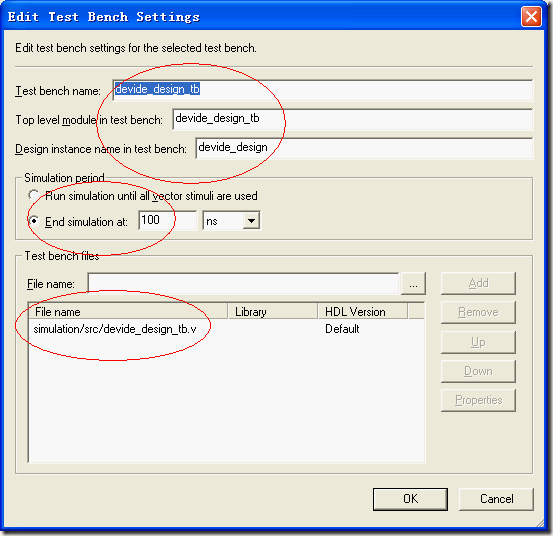

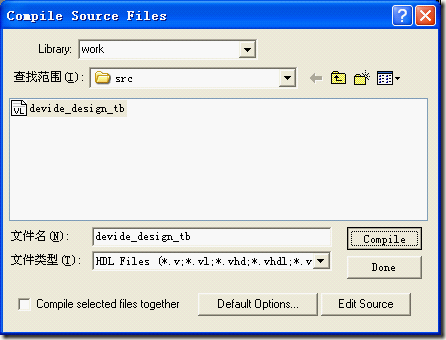

(3)添加testbench文件

(4)编译,Run RTL Simulation,即功能仿真

(5)Quartus II+Altera Modelsim会自动完成Modelsim各种各种设置,直到仿真结束,如下:

(三)时序仿真

(1)如在一开始设置中,选中在编译后自动进行门级仿真(时序仿真),软件会在编译后自动进行仿真,知道仿真结束,设置如下图:

(2)当然,也可以在功能仿真的基础上,直接Run gate level仿真即时序仿真

(3)Quartus II + Modelsim自动加载,时序仿真结果如下图所示:

(四)偷懒调试法

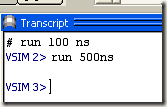

在完成功能仿真,或者时序仿真最后一步之后,Modelsim已经出现了仿真结果,此时还可以进行“深度”调试:

(1)run 500ns(你随意),用以增加仿真时间

(3)修改testbench测试文件,重新编译testbench文件,继续进行调试

(4)完了,对于庞大的工程,当然建议在Modelsim中建立工程,独立运行。预知结果如何,倾听下回分解!

posted on 2012-03-02 09:49 CrazyBingo 阅读(14748) 评论(0) 编辑 收藏 举报