第四章 随心所欲——DIY 系统板

就算你代码再怎么牛逼,硬件描述语言再怎么熟练,没有认知FPGA的工作原理,一切都是浮云。因此,在真正开始实战演练之前,Bingo将首先介绍FPGA最小工作配置要求,以及一些基本的外设,并通过DIY CPLD/FPGA系统板案例的分析讲解,用浅显易懂的语言,让初学者深刻认识CPLD/FPGA的工作原理,能够有一个更深刻的软硬件思维。

一、Altium Designer 09 winter 软件介绍

Layout的软件有很多,包括Altium Designer、PADS、Cadence等。Altium Designer是入门比较简单,也在一些基本场合应用较多的软件。国内大学生,很大一部分上都应用了这款软件,此处以此为平台设计CPLD/FPGA系统板。由于本软件不是本书的主要内容,因此如何安装在此处略去。

二、Altium Designer 09 winter 软件使用

Altium Designer软件已更新到2010,由于Bingo长期使用09版本,故本书中以Winter 09作为Layout平台,不再添加新版本描述的累赘。以下是Bingo发现或者总结的关于Altium Designer的部分精髓,如果您是一个初学者,请仔细看每一篇博文,希望对你有用:

(1)Altium Designer Winter 09 Rulse Design:

http://blog.chinaaet.com/detail/16592.html

http://www.cnblogs.com/crazybingo/archive/2011/02/21/1959864.html

http://blog.chinaaet.com/detail/11114.html

http://www.cnblogs.com/crazybingo/archive/2010/07/29/1788161.html

(3)TMD的Altium Designer的自我阉割功能:

http://blog.chinaaet.com/detail/18161.html http://www.cnblogs.com/crazybingo/archive/2011/03/10/1979418.html

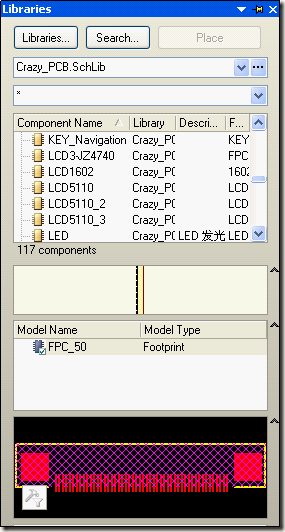

对于本章节关于Layout的阐述,都建立在Altium Designer winter 09平台, 以及Bingo DIY 元件库Crazy_PCB.lib。此库为Bingo大学2年Layout的项目经验,通过点点滴滴的积累下来的DIY 封装库,所有元件都通过测试,并且应用在多项项目中,下载地址为:

http://www.chinaaet.com/lib/detail.aspx?id=86259

读者若有兴趣,可以自行下载;若有问题,可以联系Bingo,随时更新库文件。

最后,推介一个PCB Layout的知名论坛,希望对PCB学习者有用:

三、Step By Step DIY CPLD核心板

再怎么牛逼的代码设计能力,作为一个硬件工程师,如果自己不会设计版图,或者说完全不懂硬件平台的架构,而是以购买人家的系统板作为平台,相应的在上面实现功能,这未免有太大的依赖性;同时,对于创造发挥也有一定的局限性。在公司可以有严格的分工,固定员工负责某部分的技术。但对于电子信息的初学者而言,就算你一味写代码,了解或者掌握基础的硬件设计,将会对软件有更深刻的理解和构思,所谓“硬件是软件的平台”,没有平台,灵魂没有肉体。

以下是Bingo在学习过程中的两个小设计,借此以浅俗易懂的语言,介绍CPLD/FPGA的工作原理以及核心系统版设计,希望对读者有一定的帮助。

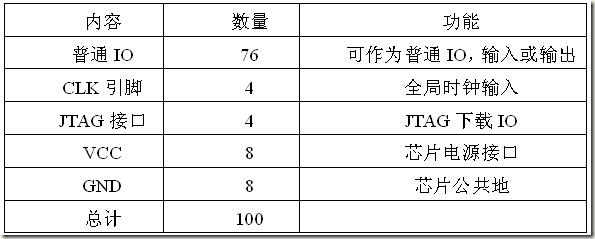

1. EPM240T100C5N 引脚介绍

MUX II数据手册下载地址:http://www.altera.com.cn/literature/lit-max2.jsp

EPM240T100C5N IC 引脚介绍:

2. EPM240T100C5N 工作条件

(1)VCC = 3.3V, GND = 0V

(2)4个CLK全局时钟接口至少有一个输入作为驱动时钟

(3)JTAG接口,用来烧录代码

注意:MUX II 可以不用外部晶振,因为MUX II 内部有一块UFM,可作为内部晶振,能够达到10M的频率(不是很准确),具体再次不做阐述,有兴趣的可以参考Bingo的笔记:

http://blog.chinaaet.com/detail/20822.html

http://www.cnblogs.com/crazybingo/archive/2010/05/14/1735338.html

3. EPM240T100C5N 核心板设计

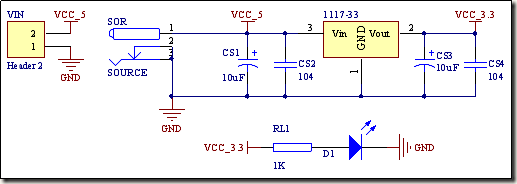

(1)电源模块

a) 由于CPLD内核工作需要3.3V电压,因此电源模块需要能提供3.3V电源,由AMS1117-3.3直接产生,供给FPGA VCCIO。电路图如下所示:

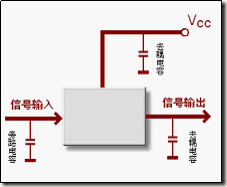

b) 由于PLD工作频率之高,为了得到更稳定的时候,更稳定的工作状态,提供更稳定的电源,需要在每个VCC接口下拉一个104的电容。如下图所示:

关于并联电容有如下作用:

此处为去耦电容,去藕电容就是起到高频信号提供回流路径,就是去除高频耦合,满足驱动电路电流的变化,避免相互间的耦合干扰 ;同时也有滤波的作用(根据TI的模拟设计方案,若是几百兆的频率工作,最好同时并联103一下的电容,已达到更好的状态)。

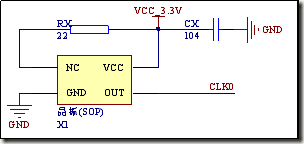

(2)时钟模块

时钟是CPLD工作的必须条件(除非在要求不高的场合,使用内部UFM),用50MHz的晶振产生时钟源,供给CPLD,作为驱动时钟。其电路如下所示:

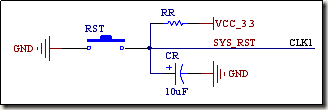

(3)复位模块

考虑到电路的稳定性,工作的可控性,在电路板中一般都设定复位模块,来实现硬件的异常复位或者重新开始工作。具体电路图如下所示:

注意:复位信号与CPLD的全局时钟输入IO相连,这并不意味着只能连全局时钟,只是全局时钟连接能够达到更大的同步性以及可控性,而一般IO是具有局部性,在时序要求相当严格的场合,这样更保险。

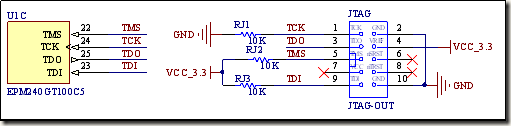

(4)JTAG模块

保证一个模块的运行,这理所当然需要一个灵魂。而这个灵魂的通道,就是JTAG接口。JTAG和PC通信,烧录配置信息。具体电路图如下所示:

4. CPLD核心板Layout注意事项

(1)每一个VCC的去耦电容要尽可能靠近端口,以达到更好的去耦效果

(2)JTAG接口4条信号线,大致保持等长,保证信号完备性

(3)晶振尽可能靠近IC,CLK输入信号线不能与IO信号线平行

(4)电源尽量做到数模隔离,减少干扰

(5)必要时加上防短路电路

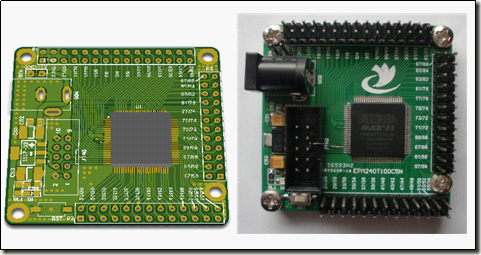

5. CPLD核心板实物图

若有需要参考原理图的读者,请下载Bingo设计的原理图,下载地址为:

http://www.chinaaet.com/lib/detail.aspx?id=86263

注:原理图见附件。

四、Step By Step DIY FPGA系统板

1. EP2C8Q208C8N 引脚 介绍

Cyclone II数据手册下载地址:http://www.altera.com.cn/literature/lit-cyc2.jsp

EPM2C8Q208C8 引脚介绍:

相对于CPLD而言,此款型号FPGA出了引脚上增多外,多了1.2V内核电压,ASP接口,两个锁相环,以及配置方式选择引脚 MSEL。

2. EP2C8Q208C8N 工作条件

(1)VCC1 = 3.3V,VCC2 = 1.2V, GND = 0V

(2)8个CLK全局时钟接口至少有一个输入作为驱动时钟

(3)JTAG接口,用来配置FPGA

(4)ASP接口,用来烧录EPCS

(5)MSEL,用来选择工作模式(同时接地为JTAG+ASP模式)

注意1:(4)不是必须的,可以间接通过JTAG下载jic文件来配置EPCS。

注意2:对于Cyclone IV器件而言,除了IO,PLL增加以外,另需2.5V芯片工作电压;以及JTAG保护电路。本书中并没有详细介绍,详细问题的解析,请查阅Bingo的网页笔记:

http://blog.chinaaet.com/detail/18404.html

http://www.cnblogs.com/crazybingo/archive/2011/04/02/2003896.html

3. EP2C8Q208C8N 系统板设计

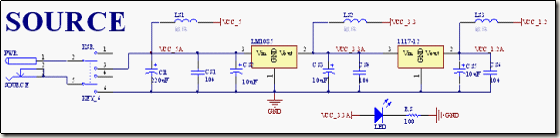

(1)电源模块

相对于CPLD而言,此款型号FPGA增添了1.2V电压产生电路,作为内核电压。具体电路图如下所示:

(2)时钟模块

同CPLD模块,此处不做过多阐述。

(3)复位模块

同CPLD模块,此处不做过多阐述。

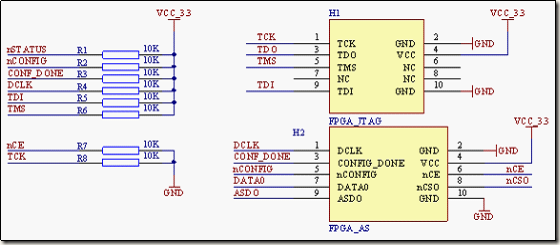

(4)JTAG模块

同CPLD模块,此处不做过多阐述。

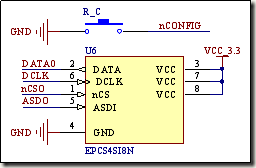

(5)ASP模块

ASP模块作为烧录pof文件到EPCS中的通道,也是PC通信的接口。具体电路图如下所示(ASP+JTAG):

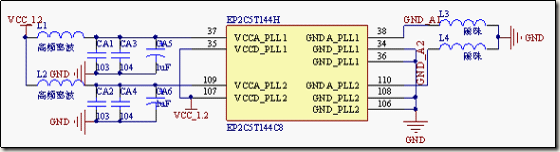

(6)PLL模块

本款芯片内置2个PLL,用来锁相,来产生复合要求的频率,增加频率稳定性和可靠性。具体电路图如下所示:

(7)EPC4 模块

EPCS4用来存储pof文件信息,用来配置FPGA,相当于单片机中的flash,用来存储启动代码。

以上(1)到(7)便是FPGA最小系统版配置,以下是作为系统板外围配置介绍。本例中以具备SDRAM,SRAM,UART等电路的系统板为题材,其余外设的具体电路图介绍如下:

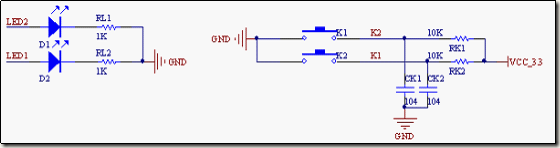

(8)按键,LED模块

按键是设备用户控制接口,作为人机交互接口;LED是指示灯显示信号,作为工作状态的反馈信号。具体电路图如下所示:

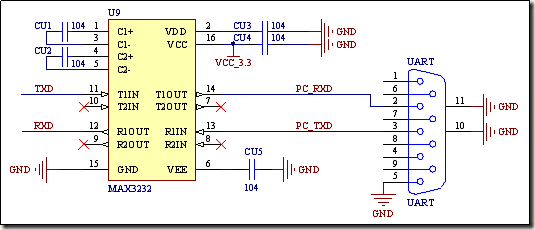

(9)串口通信模块

串口通信模块作为与PC的通信接口,通过纯硬件描述语言描述协议或者UART IP核的应用,来完成硬件与PC机的通信,人机交互的终端。具体电路图如下所示:

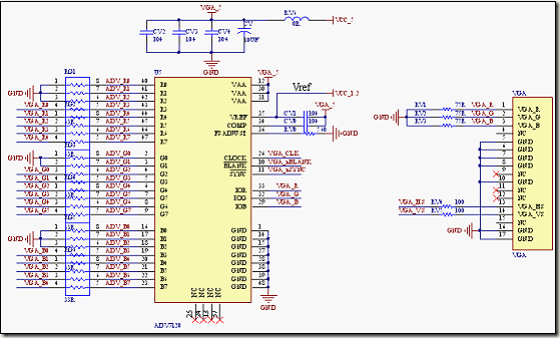

(10)VGA接口模块

VGA 15 PIN接口是专用于VGA视频信号的驱动的。由于FPGA的高速,高精度,VAG的驱动是FPGA最擅长的功能之一。此模块同时采用AD7120KST50视频转换芯片,把16bit数字信号转换为RGB565信号,从而在硬件上实现了真彩显示的要求。具体电路图如下所示:

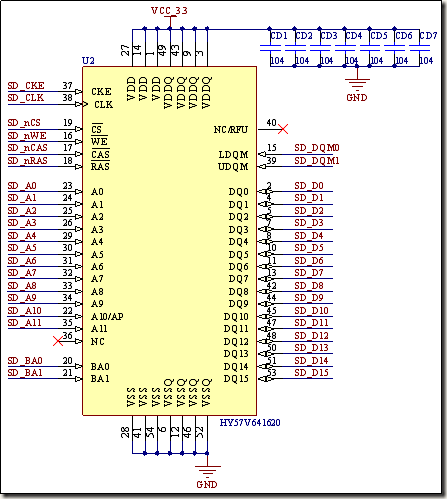

(11)SDRAM存储模块

此模块作为FPGA片上系统(SOPC)的内存,同时也可以作为VGA显示的显存,总之有大容量存储功能,主要完成FPGA海量数据的存储和搬运。具体电路图如下所示:

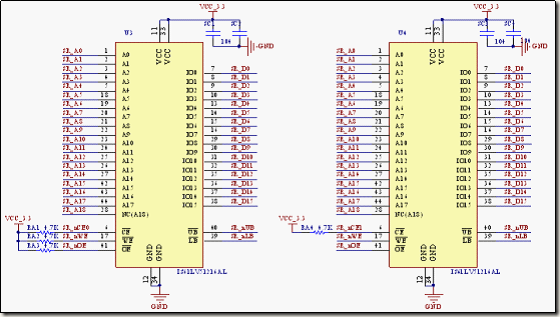

(12)SRAM存储模块

SRAM是掉电丢失存储芯片,一般用来作为液晶显存,配合VGA刷屏工作;同时在片上系统中,在容量大小满足的情况下,也可以作为内存使用。本设计中为了扩大SRAM内存,用两片SRAM串联的形式来达到目的。具体电路图如下所示:

注意:没有用nand flash的原因,是因为EPCS4,EPCS16对于一般的片上系统而言,已经足够满足了代码的容量,因此,对于一般应用,可以省略该IC,降低成本。

4. FPGA系统板Layout注意事项

(1)每一个VCC的去耦电容要尽可能靠近IO,来达到更好的去耦效果

(2)JTAG 接口4条信号线要大致等长,以保证时序的准确性

(3)ASP接口信号线要大致等长,以保证时序的准确性

(4)EPCS信号线与FPGA之间的连线要等长,以保证时序的准确性

(5)晶振尽可能靠近IC,CLK输入信号线不能与IO信号线平行

(6)电源尽量做到数模隔离,减少干扰

(7)必要时在电源输入加上反接电源。

(8)按键输入可以接在全局时钟CLK上,在节约IO的基础上,满足信号的同时性。

(9)SDRAM数据线,地址线保持基本等长,以保证时序的准确性。

(10)SRAM数据线,地址线保持基本等长,以保证时序的准确性。

(11)ADV7120信号线要求等长,保证RGB565信号的完善。

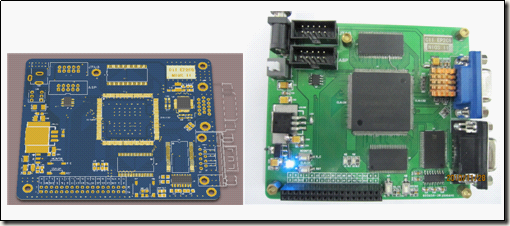

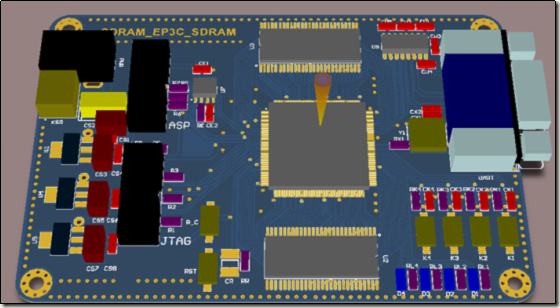

5. FPGA系统板实物图

若有需要参考原理图的读者,请下载Bingo设计的原理图,下载地址为:http://www.chinaaet.com/lib/detail.aspx?id=86263

Cyclone II

Cyclone III

posted on 2011-07-26 13:30 CrazyBingo 阅读(7162) 评论(2) 编辑 收藏 举报