Avalon-MM____SRAM IP Design

存储器SRAM的Avalon-MM设计,根据SRAM:IS61LV51216AL-10TI 数据手册,设计如下Avalon-MM接口

(1)verilog代码

module Crazy_SRAM

#(

parameter DATA_LEN = 16,

parameter ADDR_LEN = 19

)

(

input csi_clk,

input csi_reset_n,

//

input [(ADDR_LEN-1) : 0] avs_address,

input [(DATA_LEN/8-1): 0] avs_byteenable_n,

input avs_write_n,

input [(DATA_LEN-1) : 0] avs_writedata,

input avs_read_n,

output [(DATA_LEN-1) : 0] avs_readdata,

//

inout [(DATA_LEN-1) : 0] coe_SRAM_DQ, // SRAM Data bus 16 Bits

output [(ADDR_LEN-1) : 0] coe_SRAM_ADDR, // SRAM Address bus 19 Bits

output coe_SRAM_LB_N, // SRAM Low-byte Data Mask

output coe_SRAM_UB_N, // SRAM High-byte Data Mask

output coe_SRAM_CE_N, // SRAM Chip chipselect

output coe_SRAM_OE_N, // SRAM Output chipselect

output coe_SRAM_WE_N // SRAM Write chipselect

);

assign coe_SRAM_DQ = coe_SRAM_WE_N ? 'hz : avs_writedata;

assign avs_readdata = coe_SRAM_DQ;

assign coe_SRAM_ADDR = avs_address;

assign coe_SRAM_WE_N = avs_write_n;

assign coe_SRAM_OE_N = avs_read_n;

assign coe_SRAM_CE_N = avs_read_n & avs_write_n;

assign {coe_SRAM_UB_N, coe_SRAM_LB_N} = avs_byteenable_n;

endmodule

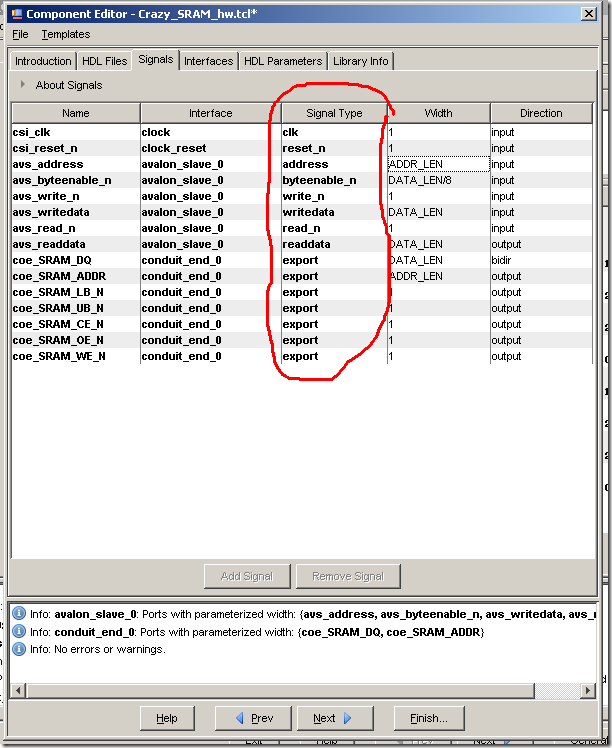

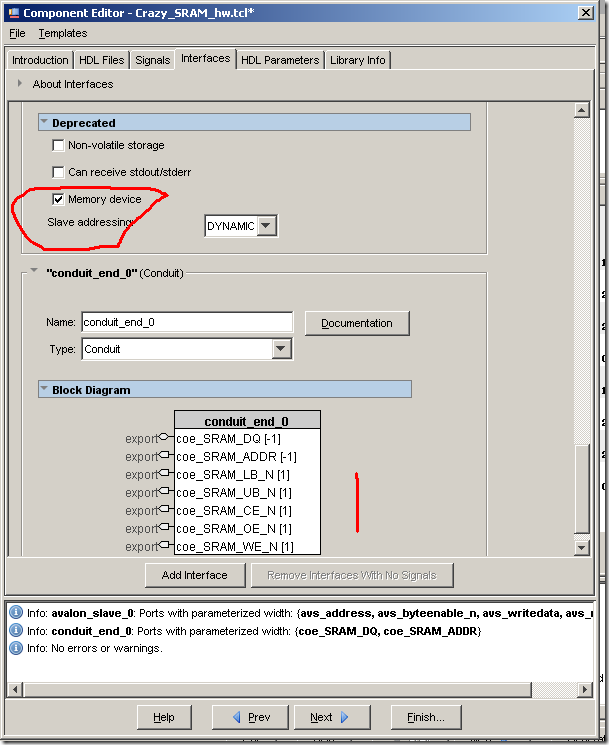

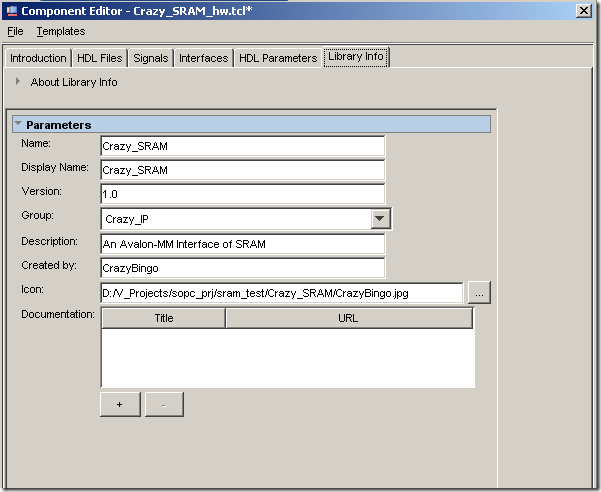

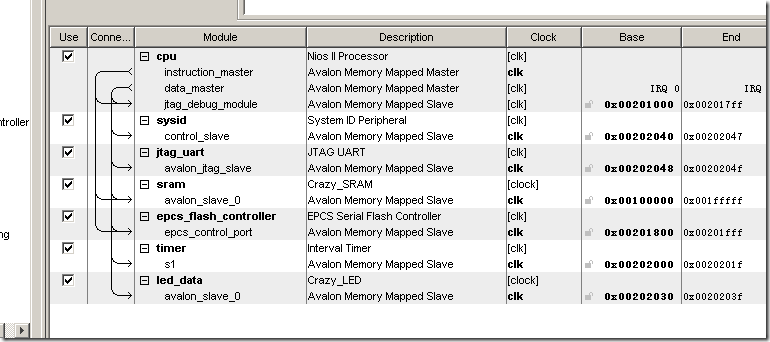

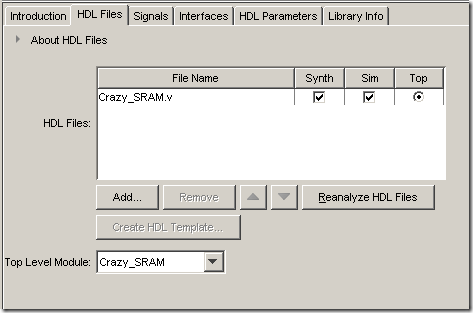

(2)在SOPC中添加

(3)Quartus II 中建立工程 ,分配引脚,编译

module sram_test

(

//global clk

input clk,

input rst_n,

//sram interface

inout [15:0] sram_data,

output [18:0] sram_addr,

output sram_ce_n,

output sram_we_n,

output sram_oe_n,

output sram_ub_n,

output sram_lb_n,

//led interface

output [1:0] led_data

);

sram_test_core sram_test_core_inst

(

.clk (clk),

.reset_n (rst_n),

.coe_SRAM_ADDR_from_the_sram (sram_addr),

.coe_SRAM_CE_N_from_the_sram (sram_ce_n),

.coe_SRAM_DQ_to_and_from_the_sram (sram_data),

.coe_SRAM_LB_N_from_the_sram (sram_lb_n),

.coe_SRAM_OE_N_from_the_sram (sram_oe_n),

.coe_SRAM_UB_N_from_the_sram (sram_ub_n),

.coe_SRAM_WE_N_from_the_sram (sram_we_n),

.coe_data_from_the_led_data (led_data)

);

endmodule

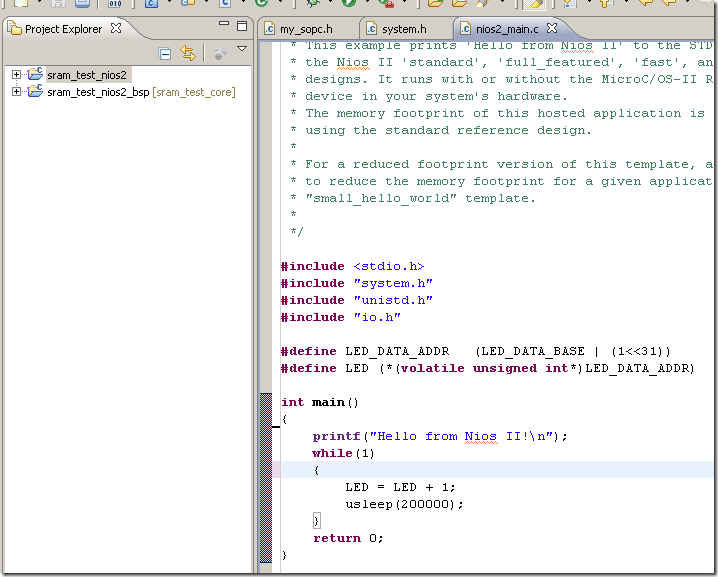

(4)建立nios2 工程

(5)run handware, 搞定

继续,walk when before i can fly。。。。

posted on 2011-02-27 22:32 CrazyBingo 阅读(2190) 评论(2) 编辑 收藏 举报