FPGA_MCU双系统系复位冲突

FPGA_MCU双系统系复位冲突

郁闷了1天,为什么不行呢,苍天无眼,我该如何面对……

不就是想通过单片机给个信号嘛,使得Verilog工程里面的某些变量复位,使得MCU—FPGA联调更加的智能和谐,可是,可是……

为啥仿真行的,实际验证就一直为0,一直就不行了呢?

郁闷省略号……

请见下文:

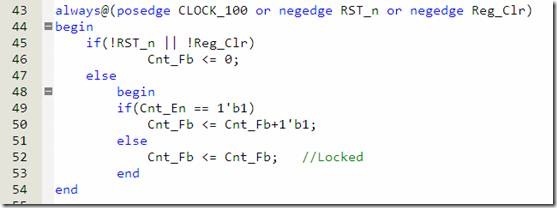

RST_n是FPGA本身板载按键信号,Reg_Clr是MCU给的信号,但是为什么不行呢??

曾经听一位老师说过,系统联调,双时钟冲突,使得数据缺失。那这是不是类似的问题呢:系统联调,双复位冲突,使得系统NC,是不是呢??

不知道,大概是的,至少这是一个问题,发现了,未解决,and 待解决……

难道双系统冲突真的会造成这样的后果吗?

Need more time,此问题已经避免了,下次要是再让我遇到了,我非宰了它不可!!!!!

posted on 2010-07-29 14:38 CrazyBingo 阅读(909) 评论(1) 编辑 收藏 举报