[Craftor原创]EZ-USB与FPGA的通信接口设计

声明:Craftor原创,转载请注明出处。

使用芯片:CY7C68013A(Cypress)与XC3S50AN(Xilinx)

一、原理图

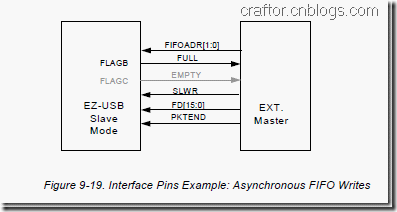

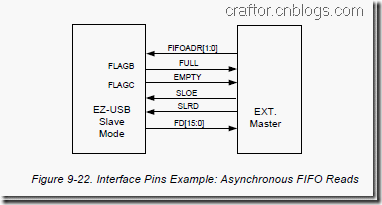

FPGA与EZ-USB通过异步FIFO方式连接,以下截图来自于Cypress的手册EZ-USB_TRM.pdf。

将图9-19和9-22两图中的信号合并在一起,与FPGA连接即可。

本例子中使用了以下信号: FIFOADR[7:0](只用了8位总线)、SLRD、SLOE、SLWR、FLAGA(配置成EP6 FULL)、FLAGB(配置成EP2 EMPTY)、PKTEND(常1)、SLCS#(常0)

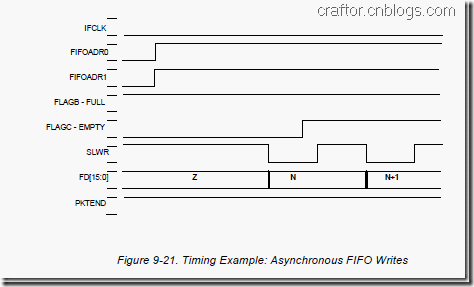

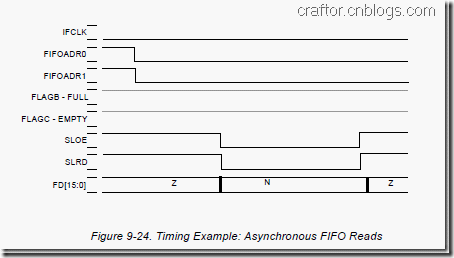

二、FPGA读写SlaveFIFO时序

异步写,在FULL不为0的时候,SLWR下降沿的时候将写的数据放到总线上,保持一个周期即可将数据写入。

异步读,在EMPTY不为0的时候,将SLOE和SLRD拉低,过半个周期读总线上的数即可。

-->附件中有原理图可以参考

三、FPGA代码

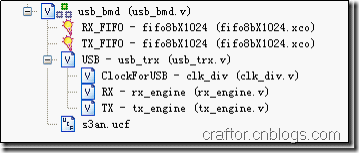

工程结构如下图,在Xilinx ISE中。

1)usb_bmd.v为顶层测试文件,测试上行和下行的数据。

2)RX_FIFO为下行数据缓存FIFO,TX_FIFO为上行数据缓存FIFO。

本工程中直接例化了FPGA内部的FIFO,可根据实际情况适当加大或减小FIFO,最小深度不得低于512。

3)usb_trx为FPGA与CY7C68013A通信的核心模块,包括:rx_engine.v下行接口,tx_engine上行接口,clk_div.v分频模块(控制FPGA读写SlaveFIFO的频率,不高于48M)。

可以根据实际电路情况调高或降低分频系数,但不建议修改,源代码中的分频系数已经为实测最佳情况,双面板没有做任何阻抗匹配的情况下,可以稳定传输数据。如果PCB阻抗做的比较好,可又适当调高试试。

4)S3an.ucf为管脚约束文件,可又根据自己的FPGA管脚进行修改。

-->附件中有Verilog源代码

二、固件程序,见附件CFR-FIFO-1.1.iic

通过CyConsole下载到外部的EEPROM中即可(在学习笔记[1]中有说明如何下载)。

该固件中使用了异步SlaveFIFO模式,使用端点EP2和EP6,512B 大小,4倍缓冲。

-->该固件仅供学习使用,源代码不公开,也不需要公开。

三、测试

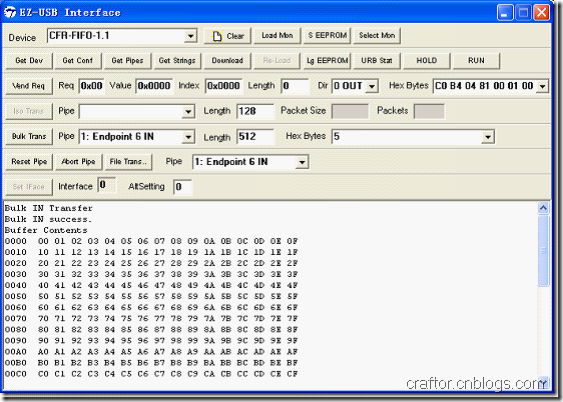

1)使用EZ-USB CyConsole,选择Endpoint 6 IN,接收到的数为00~FF。

因为在usb_bmd.v代码中,不断向TX_FIFO中写入8位的cnt,从0开始。如下图

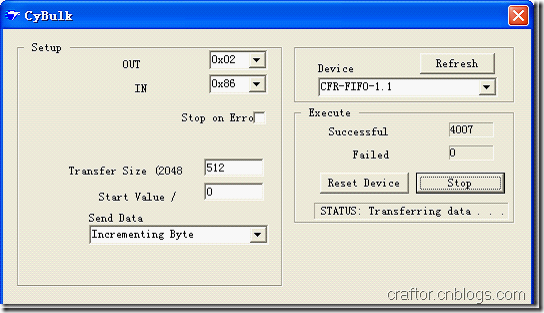

2)使用CyBulkLoop程序,进行闭环测试。数据包长度为512,从0开始累加,测试结果如下图。

细心的读者可以发现,实际在usb_bmd代码中做了手脚,上传的数据并不是真正下发的数据,而是自己上传的00~FF。

因为如果将代码中的RX和TX进行闭环,是下行一个数据(8b)立即上传一个数据的。而USB的SlaveFIFO是512B的,每次上行数据最小是512B,而且必须是512B的整数倍。在实际应用中需要注意。

附件:

浙公网安备 33010602011771号

浙公网安备 33010602011771号