软件设计师_计算机系统基础(1.1)

1.1 计算机系统基础知识

1.1.1 计算机硬件基本组成

计算机的基本硬件系统是由运算器、控制器、存储器、输入设备和输出设备五大部件组成。

运算器、控制器等部件被集成在一起统称为中央处理单元(Central Processing Unit,CPU)。

CPU是硬件系统的核心,用于数据的加工处理,能完成各种算术、逻辑运算及控制功能。

存储器是计算机系统中的记忆设备,分为内部储存器和外部存储器。前者速度高、容量小,一般用于临时存放程序、数据及中间结果。而后者容量大、速度慢,可以长期保存程序和数据。

输入设备和输出设备合称为外部设备(简称外设),输入设备用于输入原始数据及各种命令,而输出设备则用于输出处理结果

1.1.2 中央处理单元

CPU的功能

(1)程序控制。CPU通过执行指令来控制程序的执行顺序,这是CPU的重要功能。

(2)操作控制。一条指令功能的实现需要若干操作信号配合来完成,CPU产生每条指令的操作信号并将操作信号送往不同的部件,控制相应的部件按指令的功能要求进行操作。

(3)时间控制。CPU对各种操作进行时间上的控制,即指令执行过程中操作信号的出现时间、持续时间及出现的时间顺序都需要进行严格控制。

(4)数据处理。CPU通过对数据进行算术运算及逻辑运算等方式进行加工处理,数据加工处理的结果被人们所利用。所以,对数据的加工出来也是CPU最根本的任务。

2.CPU的组成

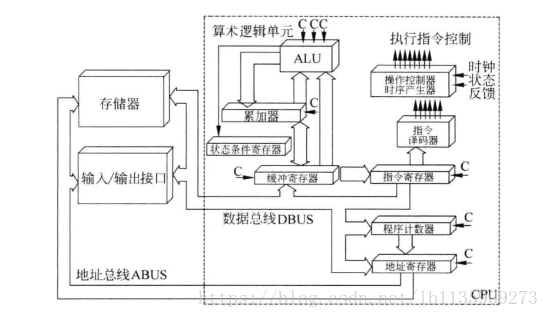

CPU主要由运算器、控制器、寄存器组合内部总线等部件组成,如图1所示。

图1 CPU基本组成结构示意图

1)运算器

运算器由算术逻辑单元(Arithmetic and Logic Unit,ALU)、累加寄存器、数据缓冲寄存器和状态条件寄存器组成,

它是数据加工处理部件,用于完成计算机的儿歌中算术和逻辑运算。相对控制器而言,运算器接受控制器的命令而进行动作,即运算器所进行的全部操作都是由控制器发出的控制信号来指挥的,所以它是执行部件。运算器有如下两个主要功能。

(1)执行所有的算术运算,如加、减、乘、除等基本运算及附加运算。

(2)执行所有的逻辑运算并进行逻辑测试,如与、或、非、零值测试或两个值的比较等。

下面简要介绍运算器中各组成部件的功能。

(1)算术逻辑单元。ALU是运算器的重要组成部件,负责处理数据,实现对数据的算术运算和逻辑运算。

(2)累加寄存器(AC)。AC通常简称为累加器,它是一个通用寄存器,其功能是当运算器的算术逻辑单元执行算术或逻辑运算时,为ALU提供一个工作区。例如,在执行一个减法运算前,先将被减数取出暂存在AC中,再从内存储器中取出减数,然后同AC的内容相减,将所得的结果送回AC中。运算的结果是放在累加器中的,运算器中至少要有一个累加寄存器。

(3)数据缓冲寄存器(DR)。在对内存储器进行读/写操作时,用DR暂时存放由内存储器读/写的一条指令或一个数据自,将不同数据段内读/写的数据隔离开来。

DR的主要作用为:作为CPU和内存、外部设备之间数据传送的中转站;作为CPU和内存、外围设备之间在操作速度上的缓冲;在单累加器结构的运算器中,数据缓冲寄存器还可建作为操作数寄存器。

2)控制器 (控制程序的顺序,指令,总线,中断等)

运算器只能完成运算,而控制器用于控制整个CPU的工作,它决定了计算机运行过程的自动化。它不仅要保证程序的正确执行,而且要能够处理异常事件。

控制器一般包括指令控制逻辑、时序控制逻辑、总线控制逻辑和中断控制逻辑等几个部分。

指令控制逻辑要完成取指令、分析指令和执行指令的操作,其过程分为取指令、指令译码、按指令操作码执行、形成下一条指令地址等步骤。

(1)指令寄存器(IR)。当CPU执行一条指令时,先把它从内存储器取到缓冲寄存器中,在送入IR暂存,指令译码器根据IR的内容产生各种微操作指令,控制其他的组成部件工作,完成所需的功能。

(2)程序计数器(PC)。PC具有寄存信息和计数两种功能,又称为指令计数器。程序的执行分两种情况,一是顺序执行,二是转移执行。在程序开始执行前,将程序的起始地址送入PC,该地址在程序加载到内存时确定,因此PC的内容即是程序的第一条指令的地址。执行指令时,CPU将自动修改PC的内容,以便使其保持的总是将要执行的下一条指令的地址。由于大多数指令都是按顺序来执行的,所以修改的过程通常只是简单地对PC加1。

当遇到转移指令时,后继指令的地址根据当前指令的地址加上一个向前或向后转移的位移量得到,或者根据转移指令给出的直接转移的地址得到。

(3)地址寄存器(AR)。AR保存当前CPU所访问的内存单元的地址。由于内存和CPU存在着操作速度上的差异,所以需要使用AR保持地址信息,直到内存的读/写操作完成为止。

(4)指令译码器(ID)。指令分为操作码和地址码两部分,为了能执行任何给定的指定,必须对操作码进行分析,以便识别所完成的操作。指令译码器就是对指令中的操作码字段进行分析解释,识别该指令规定的操作,向操作控制器发出具体的控制信号,控制各部件工作,完成所需的功能。

时序控制逻辑要为每条指令按时间顺序提供应有的控制信号。

总线逻辑是为多个功能部件服务的信息通路的控制电路。

中断控制逻辑用于控制各种中断请求,并根据优先级的高低对中断请求进行排队,逐个交给CPU处理。

3)寄存器组

寄存器组可以分为 专用寄存器 和 通用寄存器。

运算器和控制器中的寄存器是专用寄存器,起作用是固定的。

通用寄存器用途广泛并由程序员规定其用途,其数目因处理器不同有所差异。

3.多核CPU

核心又称为内核,是CPU最重要的组成部分。CPU中心那块隆起的芯片就是核心,是由单晶硅以一定的生产工艺制造出来的,CPU所有的计算、接收/存储命令、处理数据都由核心执行。

各种CPU核心都具有固定的逻辑结构,一级缓存、二级缓存、执行单元、指令级单元 和 总线接口 等逻辑单元都会有合理的布局。

多核即在一个单芯片上面集成两个甚至更多个处理器内核,其中。每个内核都有自己的逻辑单元、控制单元、中断处理器、运算单元,一级Cache、二级Cache共享或独有,其部件的完整性和单核处理器内核相比 完全一致。

CPU的主要厂商AMD和Intel的双核技术在物理结构上有很大不同。AMD将两个内核坐在一个Die(晶元)上,通过直连架构连接起来,集成度更高。Intel则是将放在不同核心上对的两个内核封装在一起,因此有人将Intel的方案称为“双芯”,将AMD的方案称为“双核”。从用户端的角度来看,AMD的方案能够使双核CPU的管脚、功耗等指标跟单核CPU保持一致,从单核升级到双核,不需要更滑电源、芯片组、散热系统和主板,只需要刷新BIOS软件即可。

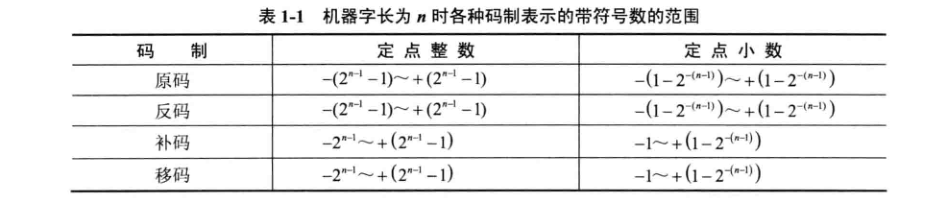

1.1.3 数据表示

机器数:计算机中的二进制数据

真值:机器数对应的实际数

机器数无符号表示正数;若约定小数点的位置在机器数的最低位之后,则是纯整数;若约定小数点的位置在机器数的最高位之前,则是纯小数。

带符号机器数,机器数的最高位表示正负符号位,其余位表示数值;同理上面的约定。

教材如下:

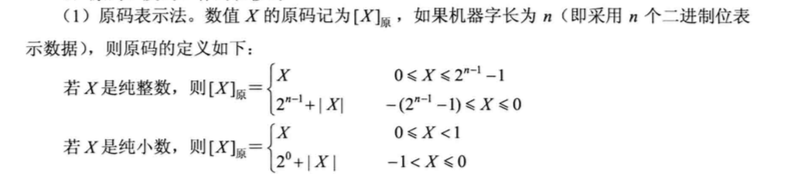

1)原码: 最高位是符号位,0表示正号,1表示负号,其余n-1位是数值的绝对值;(n表示机器长,机器数用n个二进制表示数据)

+1 原码:0 000 0001(2的0次方); -1 原码:1 000 0001

+45 原码: 0 010 1101 (2的5次方+3次方+2次方+0次方) ; -45 原码: 1 010 1101

+0.5 原码: 0.100 0000 (0.5=1/2,即2的-1次方),小数点后表示2的-1,-2,-3 ...次方 ;

-0.5 原码: 1.100 0000 (教材上用1◇100 0000 , ◇表示小数点的位置)

数值0原码两种表示:+0 原码: 0 000 0000 ;-0 原码: 1 000 0000

教材如下:

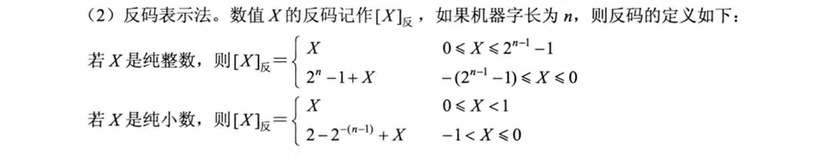

2)反码 :最高位是符号位,0表示正号,1表示负号 ;正数的反码=原码相同,负数的反码是绝对值按位求反;

+1:反码 (即原码) :0 000 0001 ; -1反码:1 111 1110 (也就是+1的所有位取反,因为最高位表示正负也相反)

+0.5 反码: 0 ◇100 0000 ; -0.5 反码: 1 ◇011 1111 (教材上用 ◇表示小数点的位置)

数值0原码两种表示:+0 反码: 0 000 0000 ;-0 反码: 1 111 1111

教材如下:

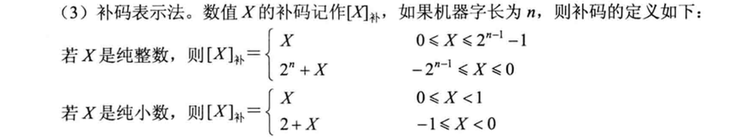

3)补码:最高位是符号位,0表示正号,1表示负号 ;正数的补码=原码=反码 ;负数补码=反码末尾+1 ;

+1 补码:0 000 0001 ; -1 补码 :1 111 1111 (反码:1 111 1110 +1)

+45补码:0 010 1101 ; -45补码 :1 101 0011

0.5 补码: 0 ◇100 0000 ; -0.5 补码: 1 ◇100 0000(反码: 1 ◇001 1111+1 需要向前面进位, 教材上用 ◇表示小数点的位置)

数值0 有唯一的编码:+0 补码:0 000 0000 ; -0 补码: 0 000 000

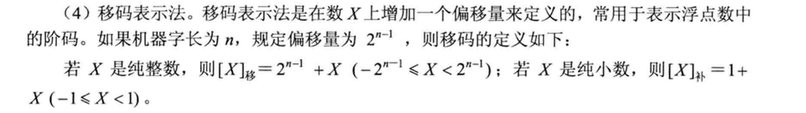

教材如下:

4)移码 : 实际上只需要将补码的符号位取反 即可得到相应的移码

+1 移码:1 000 0001 ( +1的原码0000 0001,需要偏移2的7次方,对于纯正数来说直接,是直接在首位加1);

-1 移码: 0 111 1111 ( -1 + 128 【2的7次方】-> 127 ,对于负数来说需要先加偏移量,再转换成二进制)

+45 移码:1010 1101 ; -45 移码:0 101 0011 (-45补码: 1 101 0011 )

+0.5 移码:1 ◇100 0000 ;(补码: 0 ◇100 0000 ,转换成1+0.5=1.5,对于正纯小数来说移码是最高位换成1 ),

-0.5 移码:0 ◇100 0000 ;(补码: 1 ◇100 0000 ,转换成1+【-0.5】=0.5 ),

+0 移码:1000 0000 ; -0 移码:1000 0000

2)定点数和浮点数

教材:

溢出:数值超出了指定数据类型的表示范围

一个二进制数N通常表示为如下形式:

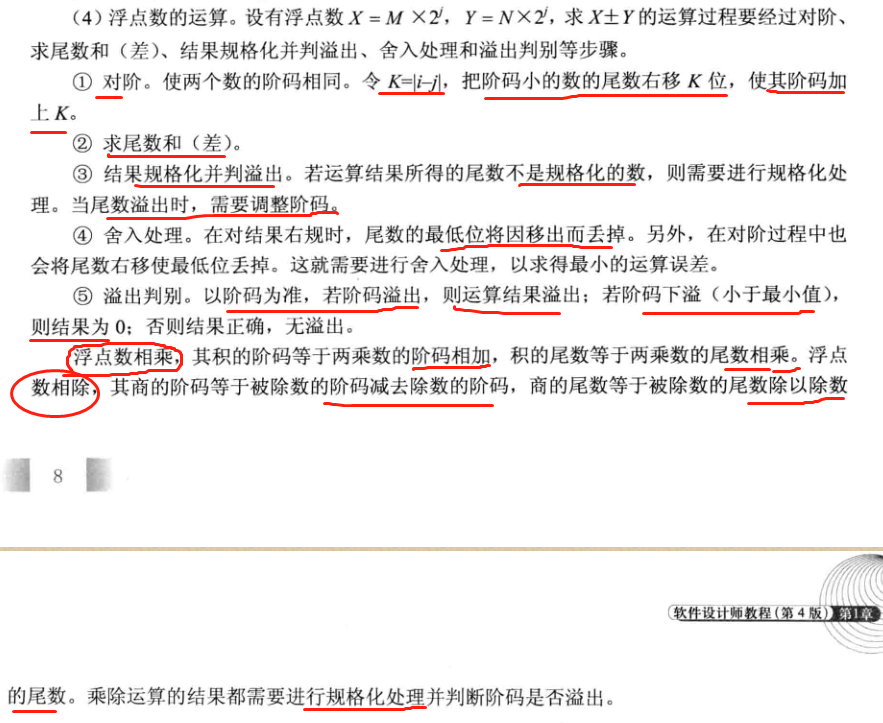

其中E称为阶码,F称为尾数。用阶码和尾数表示的数叫做浮点数,这种表示数的方法称为浮点表示法。

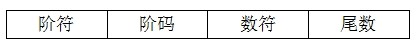

在浮点表示法中,阶码E通常是带符号的纯整数,尾数F是带符号的纯小数,表示格式如下:

在浮点表示法中,阶码决定数值范围,尾数决定数值精度。通常采用规格化浮点数来比表示尾数,将尾数的绝对值限制在区间[0.5, 1],从而表示更多的有效数字。当尾数用补码表示时,需要注意下述问题:

· 若尾数,则其规格化的尾数形式为:F=0.1×××…×,其中×可为0,也可以为1,即将尾数限定在区间[0.5,1].

· 若尾数,则其规格化的尾数形式为:F=1.0×××…×,其中×可为0,也可以为1,即将尾数限定在区间[-1,-0.5].

如果浮点数的阶码(包括一位阶符)用R位移码来表示,尾数(包括一位数符)用M位补码表示,则这种浮点数的表数范围为:

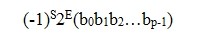

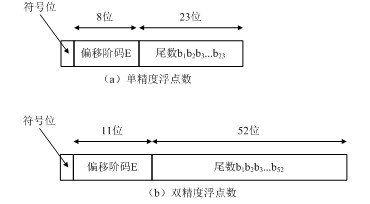

很明显,一个数的浮点表示法不唯一,这就容易导致不同计算机之间数据格式的不兼容性。为此,IEEE制定了浮点数表示的工业标准IEEE754,被广泛使用。该标准表示形式如下:

其中,(-1)S称为数符,当s为0时表示正数,当s为1时表示负数;

E为阶码,用移码表示;

(b0b1b2…bp-1)是尾数,用原码表示,p是尾数的长度,它表示尾数共p位。

目前,计算机中主要使用3种形式的IEEE754浮点数,如表1-3所示。

表1-3 三种不同类型的IEEE754浮点数

单精度、双精度浮点数格式如图1-10所示,从中可以看到IEEE754中的尾数较高位b0总是1,而且它和小数点一样隐含存在,在机器中并不明确表示出来。

图1-10 单精度、双精度IEEE754浮点数格式

精度转换: (先转成二进制,再格式化)

例如,将十进制数178.125表示成单精度浮点数。

首先将178.125表示成二进制形式:(178.125)10=(10110010.001)2,

再将二进制实数表示成规格化形式:10110010.001=1.0110010001×27 .

所以符号位s=0,

尾数=01100100010000000000000, (P长23位)

阶码E=(7+127)10=(134)10=(10000110)2. (127是上表中的偏移量)

即十进制数178.125对应的单精度浮点数形式为:

又如,可以根据下述单精度浮点数,求出其对应的十进制数值。

指数=E-127=(01111110)2-127=126-127=-1, 尾数=1.1011, 所以该浮点数的数值为1.1011*2-1=(0.11011)2=(0.84375)10. (b0=1??)

1.1.3). 二-十进制编码

用4位二进制代码表示1位十进制数,称为二-十进制编码,简称BCD编码。根据4位代码中每一位是否有确定的权来划分,可分为有权码和无权码两类。

应用最多的有权码是8421码,即4个二进制位的权从高到低分别为8、4、2和1. (普通二进制??)

无权码中用得较多的是余3码和格雷码。

余3码是在8421码的基础上,把每个数的代码加上0011后构成的。

格雷码的编码规则是相邻的两个代码之间只有一位不同。

常用的8421BCD码、余3码、格雷码与十进制数的对应关系如表1-4所示。

表1-4 8421BCD码、余3码、格雷码与十进制数的对应关系

1.1.4). 字符表示法

字符编码就是为每个字符确定一个对应的整数值,以及相对应的二进制编码。

常用的字符编码标准有ASCII字符编码标准以及IBM公司提出的EBCDIC代码等,其中ASCII码的应用范围最广。

国际标准化组织(ISO)和我国都颁布了与ASCII编码一致的编码(ISO-646和GB-1988-80)。

ASCII码采用7个二进制位对字符进行编码:低4位组d3d2d1d0用作行编码,高3位组d6d5d4用作列编码,其格式如图1-11所示。

图1-11 ASCII码编码格式

采用7位编码构成的ASCII码基本字符集只能表示128个字符,不能满足信息处理的需要,所以对ASCII码基本字符集进行扩充,

采用一个字节(8位二进制数)表示一个字符,一共可以表示256种字符和图形符号,称为扩充的ASCII码字符集。

1.1.5). 汉字表示法

汉字种类繁多,编码比拼音文字困难,而且在同一汉字处理系统中,输入、内部处理、存储和输出对汉字代码的要求不同,所以编码也不相同,关键是要进行一系列汉字代码转换。

按照计算机中汉字处理流程,汉字编码一般分成输入码、内部码和字形码三种。

(1)输入码。输入码的作用是考虑如何把汉字输入到计算机内,常用输入码包括下述四种:

· 数字编码:用一串数字来表示汉字的编码方法。

· 字音编码:一种基于汉语拼音的编码方法。

· 字形编码:将汉字字形分解归类,得到基本字形,汉字由基本字形组成。

· 形音编码:吸取了字音编码和字形编码的优点。

在上述输入码基础上,近年来,基于统计和学习功能的、以词语(短语)或句子作为输入单位的输入方法效率高,很受用户欢迎。

输入码和内部码、字形码属于完全不同的范畴,使用不同的输入码输入同一个汉字,它们对应的内部码、字形码完全相同。

(2)内部码。汉字内部码(简称汉字内码)是在设备和信息处理系统内部存储、处理、传输汉字用的代码,这种代码仅仅存在于中文计算机中。

1981年我国颁布了《信息交换用汉字编码字符集·基本集》(GB2312-80),在其中规定了汉字国标码,它采用两个字节存放一个汉字的内码,每个字节使用低7位,为了与标准ASCII码兼容,每个字节只使用94个编码。

GB2312-80国标字符集由三部分组成。

第一部分是字母、数字和各种符号,共682个;

第二部分是一级常用汉字,共3755个,按汉语拼音排列;

第三部分是二级常用字,共3008个,不是太常用,采用偏旁部分排列。

GB2312国标字符集构成一个二维平面,它分为94行、94列,行号称为区号,列号称为位号。每一个字符在码表中都有唯一的位置编码,

该编码就是字符所在区号(行号)及位号(列号)的二进制编码(区号在左,位号在右),称为"区位码".

但区位码并不是国标码,由于信息传输的原因,每个汉字的区号和位号必须分别加上32,构成的新代码就是国标码。

计算机中的双字节汉字与单字节西文字符经常混合在一起处理,容易混淆,所以需要对汉字信息进行标识。通常是把汉字两个字节的较高位都置为"1",置"1"后的双字节汉字编码就称为汉字"机内码",简称"内码".

为了统一地表示世界各国文字,1993年国际标准化组织公布"通过多八位编码字符集"的国际标准ISO/IEC 10646,简称UCS.它包含了中、日、韩等国的文字。微软、IBM等公司联合制定的工业标准Unicode(统一码或联合码),就是为此而提出。我国在1994年制定了与ISO/IEC 10646等同的国家标准Gb13000.

(3)字形码。汉字字形码是表示汉字字形的字模数据,通常采用点阵、矢量函数等方式来表示。

采用点阵形式时,汉字字形码就是这个汉字字形点阵的代码,它采用一组排成方阵的二进制位数字来表示一个汉字。这种表示形式所占存储空间相当大。

采用矢量函数形式时,用一组直线和曲线来勾画汉字、字母和符号中笔画的轮廓,记下每一条直线和曲线的数学描述(端点及控制点坐标)。这种方式输出之前必须经过复杂的运算处理,转换成点阵形式。Windows中使用的TrueType字库采用的就是这种表示形式。

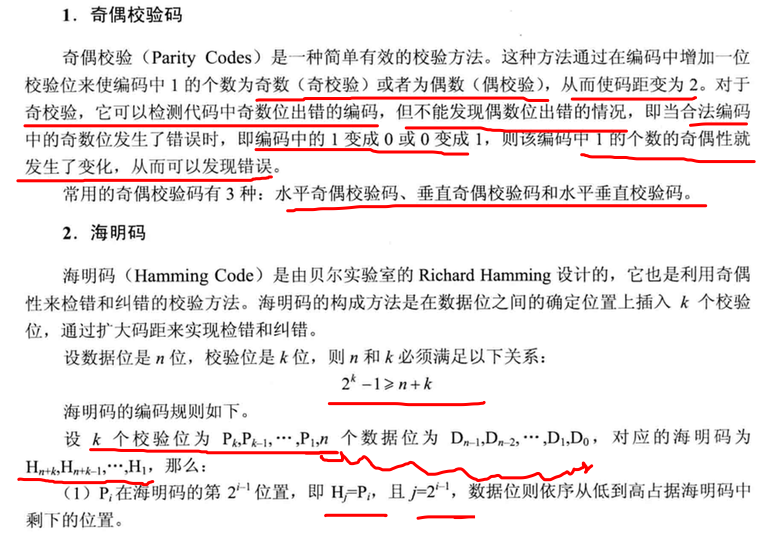

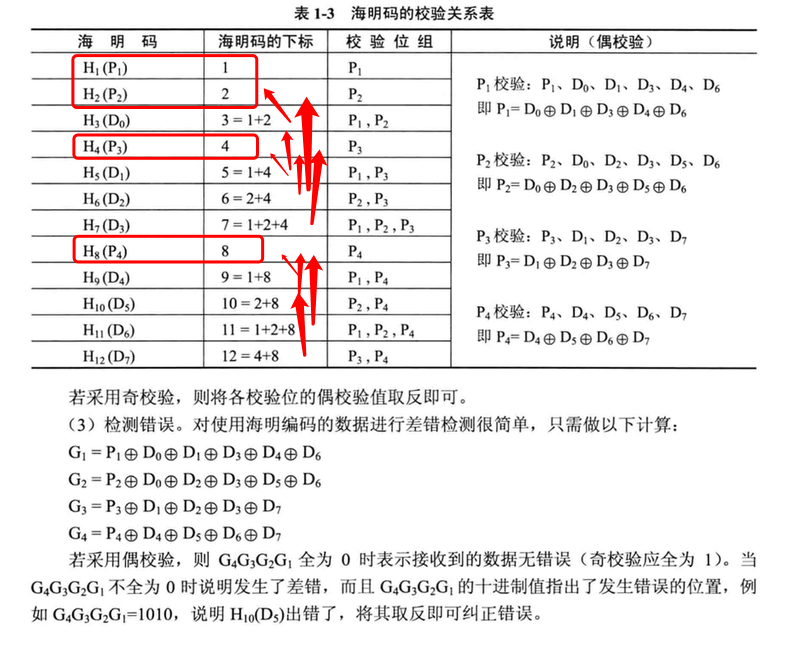

1.1.6 校验码

确保数据在传输过程中准确无误,思想是将数据分为合法编码和错误编码,如果合法编码出错会变成错误编码,这样可以检测出数据是否有错。

常见的三种:奇偶校验码,海明码,循环冗余校验码。

1)奇偶校验码

· 水平奇偶校验码。对每一个数据的编码添加校验位,使信息位与校验位处于同一行。

· 垂直奇偶校验码。这种校验方法把数据分成若干组,一组数据占一行,排列整齐,再加一行校验码,针对每一列采用奇偶校验。

例如,对于32位数据10100101 00110110 11001100 10101011进行垂直奇偶校验,如表1-5所示。

垂直奇校验: 一列和是奇数的话,校验码是0,和是偶数的话,校验码是1 ;

垂直偶校验: 一列和是奇数的话,校验码是1,和是偶数的话,校验码是0;

表1-5 垂直校验码的例子

· 水平垂直校验码。在垂直校验码的基础上,对每个数据再增加一位水平校验位,便构成水平垂直校验码。

例如,对于32位数据10100101 00110110 11001100 10101011进行水平垂直奇偶校验,如表1-6所示。

表1-6 水平垂直校验码的例子

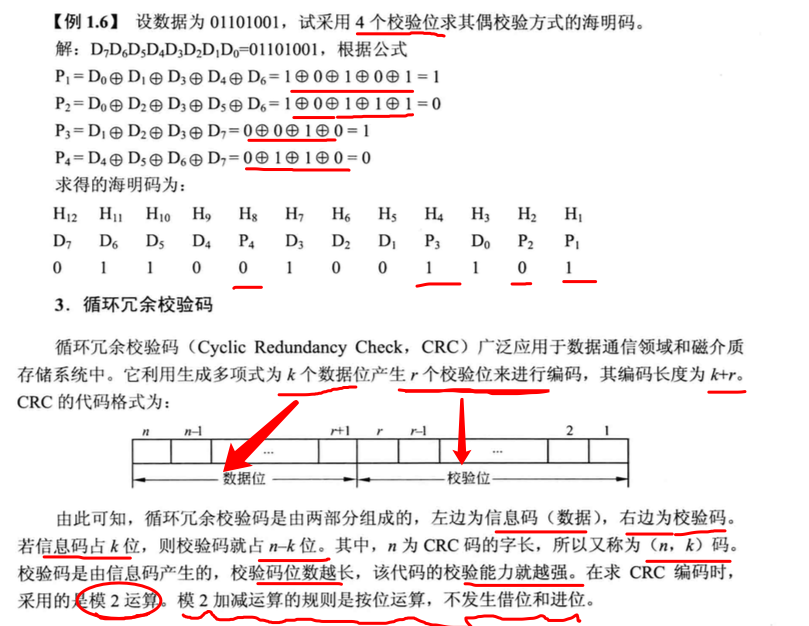

(2)循环冗余校验方法(CRC码)。

该方法能够校验传送信息的对错,并且能自动修正错误,它广泛用于通信和磁介质存储器中。如图1-12所示,CRC编码格式是在位信息后加位检验码。

图1-12 CRC编码格式

CRC码长度为n=k+r位,所以又叫做(n,k)码,用C(x)表示被传送的位二进制信息位,用G(x)表示系统的生成多项式,则构成CRC码流程如下:

上式左边就是CRC码,所以CRC码的生成过程是"左移位→除去生成多项式得到余数→加上余数".发送信息时将CRC码传送给对方,对方接收到以后除以G(x),如果传输正确,则结果为0,否则根据余数的数值确定是哪位数据出错。

浙公网安备 33010602011771号

浙公网安备 33010602011771号