一分钟理解系列—半导体存储芯片的知识点总结

在计算机的存储器中,按存储介质进行分类的话,可将存储器分成半导体存储器、磁表面存储器、磁芯存储器、光盘存储器。而除了半导体存储器中的数据易失以外,其他的存储介质都具有非易失的特性。

那么,半导体存储芯片的结构是怎样的呢?

话不多说,我们来看下吧。

半导体存储芯片的基本结构

半导体存储芯片由译码驱动电路、存储矩阵、读写电路、地址线、数据线、控制线、片选线组成。其中,译码驱动电路、存储矩阵、读写电路属于核心结构。

存储矩阵用来存储0/1代码,地址线、数据线主要用来连接CPU和外部设备。现在假设CPU或者外部设备给出地址,表示要存/取的数据在存储矩阵的哪个存储单元中,然后经过译码驱动电路,选择对应的存储单元,从而完成存/取数据。

地址线是单向的,由CPU指向存储器,或者由I/O设备的控制器指向存储器。数据线是双向的。由地址线和数据线可以计算出芯片的容量。那么如何计算呢?感兴趣的朋友可以阅读之前的这篇文章。吐血整理!这篇带你彻底理解主存中存储单元地址的分配

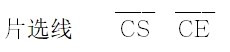

片选线,也叫做芯片选择信号,指出这次存/取操作给出的地址是不是这个存储芯片的地址。半导体存储芯片的片选线一般有两种标识方式,表示方式如下所示:

CS(芯片选择信号),CE(芯片使能信号),低电平表示有效,高电平表示无效,也就是说,如果片选线信号为低电平,则表示想要存/取的数据位于片选线所在的芯片中。

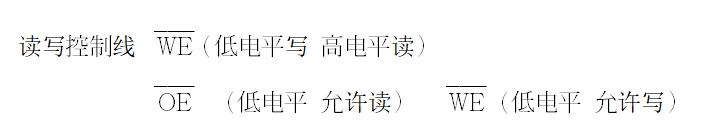

读写控制线,表示这次对半导体芯片的操作是读操作还是写操作。可以用一根线或者两根线表示,用一根线表示的话是WE,用两根线表示的话是WE和OE,具体如下所示:

存储芯片片选线的作用

接下来我们来详细讨论下存储芯片中,片选线的作用。

假设CPU现在要求用16K×1位的存储芯片组成64K×8位的存储器。如何用16K×1位的存储芯片组成64K×8位的存储器?

我们用图来看下,实际上这个问题解决并不难

16K×1表示存储容量,每个存储单元存储1位的0/1数据。那么,我们用8个这样的芯片,对8个芯片相同的地址同时进行操作,每个芯片给出1位,8个芯片就构成了16K×8的存储器。

但是,CPU要求的是64K?这个应该怎么做?

实际上,也不难,每8个芯片分成1组,然后复制4组,就构成了64K×8的存储器。

在进行读写操作时,8个芯片是同时进行工作的,所以,他们的片选线是连接在一起的。

然后对64K的空间进行划分,所以CPU的地址中0-(16K-1)的地址分配到第一组的芯片中,16K-(32K-1)的地址分配到第二组的芯片中,32K-(48K-1)的地址分配到第三组的芯片中,48K-(64K-1)的地址分配到第三组的芯片中分配到第四组的芯片中。

现在假设访问的地址是65535,进行写操作,那么这个地址表示的存储芯片应该在最后一组中,片选信号看到这个地址后,就会选择最后一组,其他三组芯片对应的片选信号是无效的,就是高电平,最后一组对应的片选信号是有效的,也就是低电平,数据就会保存在最后一组的存储芯片当中。

半导体存储芯片的译码驱动方式

译码驱动电路的作用是:在给出地址之后,根据这个地址取找到这个地址对应的存储单元。

而半导体存储芯片的译码驱动方式有两种:线选法,重合法。

我们先来看下线选法

线选法

在上图中,有A0-A3的4位地址,那么24表示有16个存储单元,那么每个存储单元可以存储多少位?图中给出的数据线是从D0-D7,一共8位。综合起来,就表示这是一个16K×8的存储器。

如何进行选择?

在上图中,地址译码器输入的是4根线,输出的16根线。给定一个输入,在输出这一端,只有一根线是有效的,只有一根线上的信号会控制相应的存储单元中的所有存储元件进行数据的输入或者输出操作。

那么在读写控制电路中,如果是读选通,就会将数据矩阵中的数据进行对外输出;如果是写选通,就会将数据写入到矩阵中的存储元件中。

现在,来看下具体工作过程:

假设地址译码器给出的地址是全0,进行译码过后,只有0这根线是有效的,其他的都是无效的。现在进行的是读操作,那么就会控制读/写控制电路打开,使得数据可以从存储矩阵输出到数据总线上。只有给定的单元才可以进行输出。

那么,线选法有没有缺点呢?缺点是什么?

在上图的译码中,地址线是4根,容量是16K×8,现在的计算机存储器,并不存在这么小的容量。

现在假设有1M×8的存储芯片,地址线有20根,经过译码器译码后就有1M条线,每给出一个地址,1M条线中,只有一条有效。而1M条线,就是1000000条线,做在芯片中将会非常密集,这么高的集成度很难做到。

所以,线选法对于容量很大的存储器来说,是个不好的方法。

接下来,来看下重合法

重合法

在线性法中,存储单元的布局方法是一个线性的数组;而在重合法中,存储单元的布局方法是二维的数组。

在重合法中,将地址分成了两部分,一部分是X,另一部分是Y,也可以叫做行列地址。行列地址分别进行译码,只能有一根线是有效的。具体工作过程:

假设给出的行列地址都是全0,行列地址进行译码后只有(0.0)这条线是有效的。只有这条线上的存储单元被选中。那么这时候,Y0这条线上的开关就会打开,数据就会通过这个开关进行数据输出。在这个过程当中,X0上的除了Y0上的存储单元的数据会进行输入以外,其他的存储单元上的数据一样会进行输出,但是,当数据经过Y31线上的开关时,由于这条线是无效的,数据会被拦截,所以,数据就输出不了,所以数据没有到数据线去。那么Y0上的除了X0的存储单元的数据会进行输入以外,其他的存储单元上的数据一样会进行输出,同样的道理,就不另外解释了。

那么,重合法的优点是什么?

在上面的线选法中,我们是假设有1M×8的存储芯片,地址线有20根,用线选法的话,经过译码器译码后就有1M条线。那么,同样的大小,我们采用重合法的话,地址线就分成两部分,每一部分都是1K条线,总计就是2K条线,那么,就比线选法进行译码的1M条少很多了,这样子,芯片就能做到很高的集成度。

结语

讲了那么多,不知道各位是不是清晰的理解了呢哈哈?

浙公网安备 33010602011771号

浙公网安备 33010602011771号