会员

周边

新闻

博问

闪存

赞助商

YouClaw

所有博客

当前博客

我的博客

我的园子

账号设置

会员中心

简洁模式

...

退出登录

注册

登录

神的随波逐流的中子

博客园

首页

新随笔

联系

订阅

管理

上一页

1

2

3

4

5

6

7

下一页

2022年3月31日

FPGA——CRC硬件电路实现及推导

摘要: 图中有32个寄存器寄存器 寄存器初值为:{R31,R30,R29...R0} 输入数据为:{C7,C6...C0} 数据先从低位输入,C0,C1,C2,C3...... | reg0 1 | reg1 1 | reg2 1 | reg3 0 | reg4 1 | reg5 1 | reg6 0 |

阅读全文

posted @ 2022-03-31 22:09 AdriftCore芯研社

阅读(565)

评论(0)

推荐(0)

2022年3月30日

FPGA——UDP包分片概述

摘要: 一、概述 以太网(Ethernet)数据帧的长度必须在46-1500字节之间,这是由以太网的物理特性决定的. 这个1500字节被称为链路层的MTU(最大传输单元). 在实际使用中,单次UDP报文传输的数据量有可能会大于1500字节,因此需要用到UDP分片技术 二、UDP分片 (1)UDP封装 (2)

阅读全文

posted @ 2022-03-30 23:20 AdriftCore芯研社

阅读(1575)

评论(1)

推荐(1)

2022年3月4日

FPGA——IDELAY应用

摘要: #1、输入延迟资源(IDELAY) 赛灵思7系列的原语IDELAY,通常用于对输入时钟数据进行时延,以满足代码时序需要。如果对FPGA代码进行时序约束,idelay会自动添加。如果没有进行时序约束就需要手动添加idleay以满足时序要求。例如在写以太网RGMII数据链路层接收端时就需要用到IDELA

阅读全文

posted @ 2022-03-04 00:02 AdriftCore芯研社

阅读(4795)

评论(0)

推荐(1)

2022年1月2日

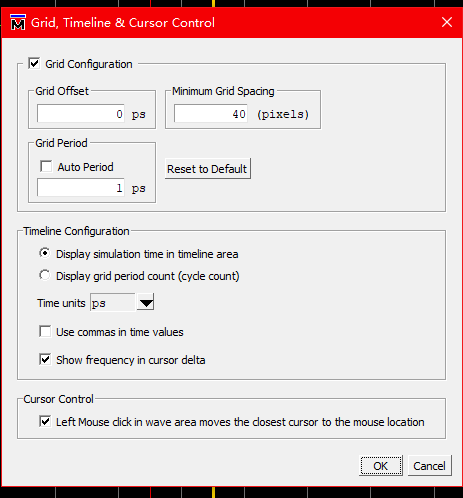

modelsim看信号频率

摘要:

评论(0)

推荐(0)

2021年12月26日

FPGA——SDRAM初探

摘要: 一、SDRAM型号及介绍 W9812G6KH 2M * 4 BANKS * 16 BITS SDRAM. Row address: A0-A11. Column address: A0-A8 SDRAM内存由BANK、Column Address、Row Address、Width组成 本次的SDR

阅读全文

posted @ 2021-12-26 19:26 AdriftCore芯研社

阅读(725)

评论(0)

推荐(0)

2021年3月2日

FPGA——RGB转灰度图像,sobel边沿检测实现及验证

摘要: 一、设计思路 采用加权平均值法 二、RGB转灰度图像代码 //RGB转灰度图像,延迟两拍输出 module rgb2gray( clk , //时钟 rst_n , //复位 rgb_vld , //rgb输入有效标识 rgb_hs , //rgb输入行信号 rgb_vs , //rgb输入场信号

阅读全文

posted @ 2021-03-02 15:06 AdriftCore芯研社

阅读(402)

评论(0)

推荐(1)

2021年2月25日

FPGA——图像采集系统摄像头传以太网实现及验证

摘要: 一、设计思路 IMAGE_SEQUENCE模块的作用是:给输入的每一行像素RGB565数据编号,并将编号的2字节数据写入FIFO,标志图像每一行像素的开始 FIFO_CTR信号状态机实现 上位机软件是大端模式,所有输入以太网MAC模块的数据应该也是大端模式 二、IMAGE_SEQUENCE模块 mo

阅读全文

posted @ 2021-02-25 16:01 AdriftCore芯研社

阅读(679)

评论(0)

推荐(0)

2021年2月23日

FPGA——vivado FIFO问题记录

摘要: (1)标准FIFO下 synchronization stage 异步时钟FIFO独有的值 表示FIFO 读时钟域的 rd_data_out开始有值的时间 当 synchronization stages = 4时 在write_data_count被写入值后,经过(synchronization

阅读全文

posted @ 2021-02-23 20:02 AdriftCore芯研社

阅读(4745)

评论(0)

推荐(1)

2021年2月22日

FPGA——以太网MAC层数据发送协议实现及验证

摘要: 一、设计思路 FPGA实现MAC层(数据链路层)的功能并连接到RTL8211物理层(PHY)芯片实现以太网数据的发送 使用GMII接口 时钟是125MHz,一次发8bit数据 8bit * 125M = 1000Mbit 所以叫做千兆以太网 RTL8211时序 来一个时钟上升沿就发一个字节的数据 数

阅读全文

posted @ 2021-02-22 16:32 AdriftCore芯研社

阅读(4586)

评论(0)

推荐(2)

2021年2月20日

FPGA——OV5640摄像头DVP接口实现及仿真

摘要: 一、设计思路 行同步计数器 场同步计数器 图像帧数计数器 摄像头输出3*3像素图像的输入信号图解 场信号vsync脉冲,表示一帧图像的开始 行信号hsync有效(高有效),摄像头输出数据 一个像素是16位数据,传入一次是8位数据,所有一个像素传了6次数据 二、代码实现 module dvp_capt

阅读全文

posted @ 2021-02-20 11:52 AdriftCore芯研社

阅读(2623)

评论(0)

推荐(0)

上一页

1

2

3

4

5

6

7

下一页

公告