FPGA基础:格雷码及FIFO应用概述

1简介

反射二进制码反射二进制码(RBC),也称为反射二进制(RB)或格雷码(Gray code),得名于Frank Gray,是二进制数制的一种排列方式,使得连续两个值之间仅有一个比特(二进制位)不同。格雷码在数字电路中的应用有助于减少误差、提高系统的可靠性,并简化逻辑操作,因此被广泛应用于各种数字系统和电子设备中。

2格雷码原理

自然二进制码

许多设备通过关闭和打开开关来指示位置。如果该设备使用自然二进制编码,位置3和4是相邻的,但二进制表示的所有三个比特都不同。自然二进制编码的问题在于物理开关并非理想的,理想的二进制码应该是连续两个值之间仅有一个比特变化。

格雷码

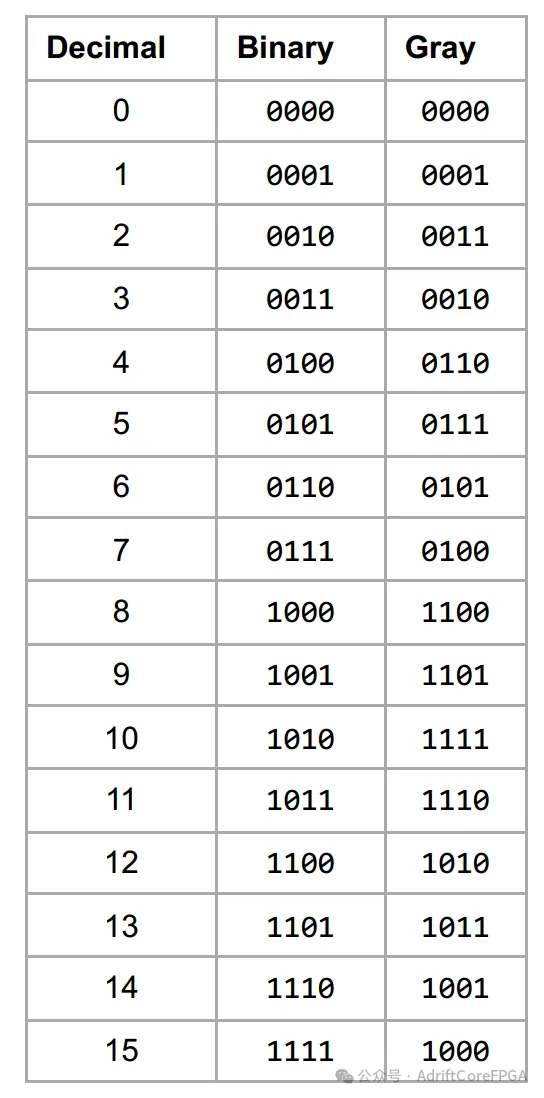

格雷码应运而生,对于十进制数,编码在仅改变一个开关的情况下会回到十进制数0。

在现代数字通信中,格雷码在错误纠正中扮演着重要的角色。例如,在诸如QAM这样的数字调制方案中,数据通常以4位或更多位的符号传输,信号的星座图被安排成相邻星座点传达的位模式仅相差一个比特。通过结合能够纠正单比特错误的前向错误纠正,接收器可以纠正导致星座点偏离到相邻点区域的任何传输错误。这使得传输系统对噪声的影响更小。

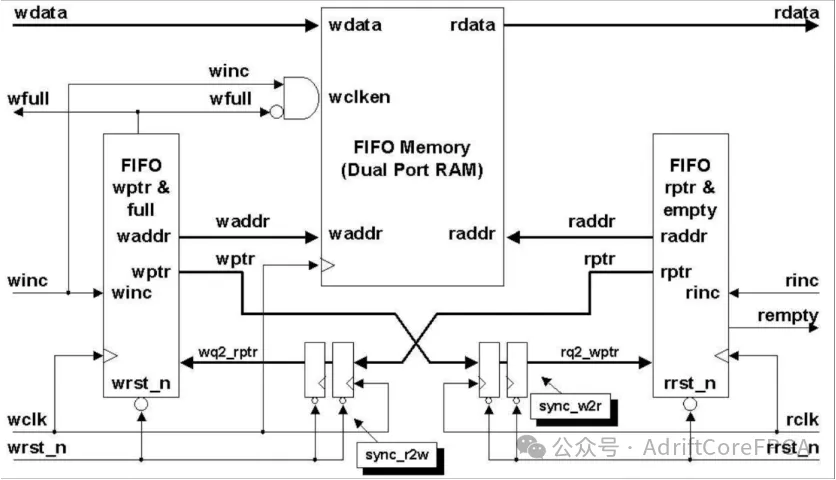

格雷码也可以用于编码跨时钟FIFO的地址,以确保在不同时钟域之间读写操作的正确执行。使用格雷码编码地址可以减少在不同时钟域之间发生的时序问题,提高跨时钟FIFO的可靠性和性能。

3格雷码在FIFO中的应用

在FIFO中,通常我们需要一个指针计数器来标识我们读取FIFO的位置。然而,在异步FIFO中,将一个时钟域中的二进制计数值同步到另一个时钟域是有问题的。这是因为一个n位计数器的每一位都可能同时改变(例如,二进制数从7变为8是0111->1000,所有位都改变了)。通常,当我们处理1位跨越时钟域的信号时,会使用多级DFF来避免亚稳态的问题。但是,如果我们有多个信号线(例如,4位计数器),并且这些信号线的延迟不一致,即skew不同,使用异步时钟采样可能导致数据不一致的问题。为了避免这一问题,FIFO计数指针的常见方法是使用格雷码计数器。格雷码每个时钟转换只允许一位改变,从而消除了尝试在同一时钟边缘上同步多个改变信号所带来的问题。

3总结

本章主要探讨了格雷码以及格雷码在FIFO中的应用,后续会进一步探讨FIFO的详细应用以及数字电路中跨时钟的处理方法。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 25岁的心里话

· 闲置电脑爆改个人服务器(超详细) #公网映射 #Vmware虚拟网络编辑器

· 基于 Docker 搭建 FRP 内网穿透开源项目(很简单哒)

· 零经验选手,Compose 一天开发一款小游戏!

· 一起来玩mcp_server_sqlite,让AI帮你做增删改查!!