一、文件读取

| 加载二进制文件 |

$readmemb("fname", mem, start_addr, finish_addr) |

|

|

fname 为数据文件名字,mem 为数组型/存储器型变量,start_addr、finish_addr 分别为起始地址和终止地址,start_addr、finish_addr 可以省略,此时加载数据的停止条件为存储器变量 mem 被填充完毕,或文件读取完毕,文件内容只应该有空白符(或换行、空格符)、二进制或十六进制数据 注释用"//"进行标注,数据间建议用换行符区分 |

|

| 加载十六进制文件 |

$readmemh("fname", mem, start_addr, finish_addr) |

|

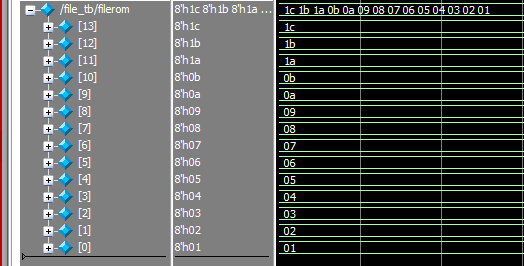

module file_tb;

reg [8-1:0] filerom [14-1:0];

initial begin

$readmemh("filetest.txt",filerom);

end

endmodule

Bin_s文件

01

02

03

04

05

06

07

08

09

0A

0B

1A

1B

1C

二、文件写入

| 系统任务 |

调用格式 |

任务描述 |

| 文件打开 |

fd = $fopen("fname", mode) ; |

fname 为打开文件的名字,fd 为返回的 32bit 文件描述符--- 正确打开时,fd 为非零值--- 打开出错时,fd为零值 |

| mode 用于指定文件打开的方式 |

|

|

| 文件关闭 |

$fclose(fd) ; |

关闭 fd 描述的对应文件 |

| mode |

描述 |

| r |

只读打开一个文本文件,只允许读数据。 |

| w |

只写打开一个文本文件,只允许写数据。如果文件存在,则原文件内容会被删除。如果文件不存在,则创建新文件。 |

| a |

追加打开一个文本文件,并在文件末尾写数据。如果文件如果文件不存在,则创建新文件。 |

| rb |

只读打开一个二进制文件,只允许读数据。 |

| wb |

只写打开或建立一个二进制文件,只允许写数据。 |

| ab |

追加打开一个二进制文件,并在文件末尾写数据。 |

| r+ |

读写打开一个文本文件,允许读和写 |

| w+ |

读写打开或建立一个文本文件,允许读写。如果文件存在,则原文件内容会被删除。如果文件不存在,则创建新文件。 |

| a+ |

读写打开一个文本文件,允许读和写。如果文件不存在,则创建新文件。读取文件会从文件起始地址的开始,写入只能是追加模式。 |

| rb+ |

读写打开一个二进制文本文件,功能与 "r+" 类似。 |

| wb+ |

读写打开或建立一个二进制文本文件,功能与 "w+" 类似。 |

| ab+ |

读写打开一个二进制文本文件,功能与 "a+" 类似。 |

| 调用格式 |

任务描述 |

| $fdisplay(fd, arguments) ; |

按顺序或条件写文件,自动换行 |

| $fwrite(fd, arguments) ; |

按顺序或条件写文件,不自动换行 |

| 输入 |

|

输入 |

|

| %h 或 %H |

十六进制格式输出 |

%c 或 %C |

ASCII 码格式输出 |

| %d 或 %D |

十进制格式输出 |

%e 或 %E |

指数格式输出 |

| %o 或 %O |

八进制格式输出 |

%f 或 %F |

浮点数 (real 型) 格式输出 |

| %b 或 %B |

二进制格式输出 |

%t 或 %T |

当前时间格式输出 |

| %s 或 %S |

字符串格式输出 |

%m 或 %M |

当前层次访问路径输出 |

| \n |

换行符 |

%% |

百分号"%" |

| \t |

制表符(Tab 键) |

\0 |

八进制代表的字符 |

| \ |

反斜杠""符 |

\0x |

十六进制代表的字符 |

| " |

双引号 |

|

|

integer fd;

integer i = 0;

reg [31-1:0] dat = 0;

initial begin

#(10 * CYCLE);

fd = $fopen("wfile.txt","w");

while(i < 10)begin

@(posedge clk)

$fdisplay(fd,"%h",dat);

dat = dat + 2;

i = i + 1;

end

$fclose(fd);

end

三、matlab交互

fid = fopen('FpgaDat.txt','r');

f = fscanf(fid,'%s');

% int

a0 = hex2dec(f(9:16));

% float

a1 = typecast(uint32(hex2dec(f(9:16))),'single');

%double

a2 = hex2num(f(9:16));

fclose(fid);

参考资料:https://www.runoob.com/w3cnote/verilog2-file.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号