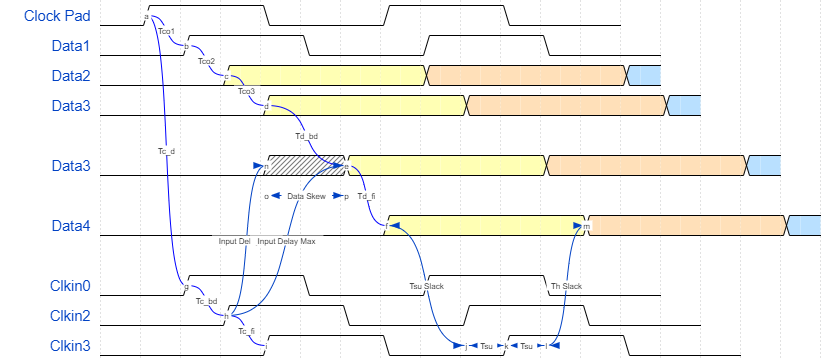

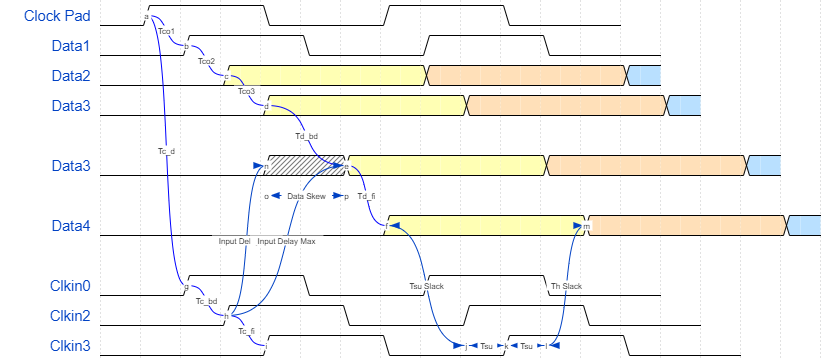

{

signal:[

{name:"Clock Pad",wave:"01..0..1..0..",node:'.a'},

{name:"Data1",wave:"0.1..0..1..0..",node:'..b'},

{name:"Data2",wave:"0..3....4....5",node:'...c'},

{name:"Data3",wave:"0...3....4....5",node:'....d'},

{},

{name:"Data3",wave:"0...x.3....4....5",node:'....n.e'},

{node:'....o.p'},

{name:"Data4",wave:"0......3....4....5",node:'.......f....m'},

{},

{name:"Clkin0",wave:"0.1..0..1..0..",node:'..g'},

{name:"Clkin2",wave:"0..1..0..1..0..",node:'...h'},

{name:"Clkin3",wave:"0...1..0..1..0..",node:'....i....jkl'},

],

edge:[

'a~b Tco1',

'b~c Tco2',

'c~d Tco3',

'd~e Td_bd',

'e~f Td_fi',

'a~g Tc_d',

'g~h Tc_bd',

'h~i Tc_fi',

'j<->k Tsu',

'k<->l Tsu',

'f<~>j Tsu Slack',

'l<~>m Th Slack',

'h~>n Input Delay Min',

'h~>e Input Delay Max',

'o<->p Data Skew',

]

}