FPGA——SDRAM初探

一、SDRAM型号及介绍

- W9812G6KH

- 2M * 4 BANKS * 16 BITS SDRAM. Row address: A0-A11. Column address: A0-A8

- SDRAM内存由BANK、Column Address、Row Address、Width组成

本次的SDRAM有4个BANK,每个BANK深度为2M,宽度为16bits,内存共有4X2X16 = 128MBits

深度由行和列组成,行有2^12 = 4K 列有2**9 = 0.5K,则深度有4K * 0.5K = 2M

- SDRAM内存由BANK、Column Address、Row Address、Width组成

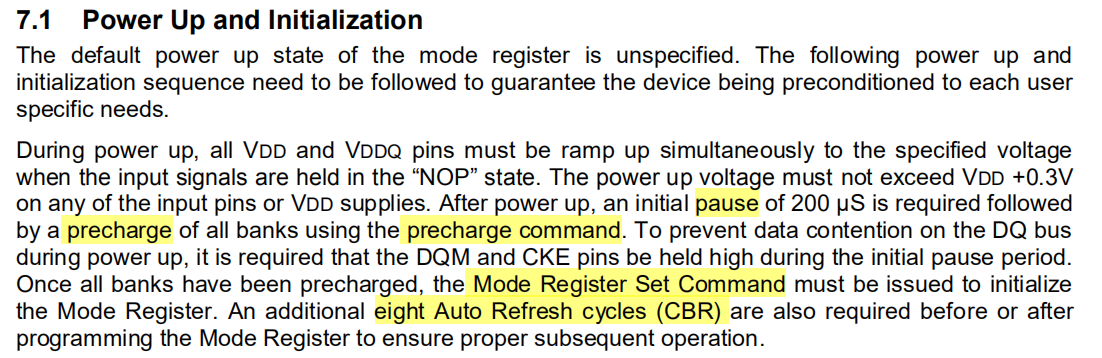

二、SDRAM初始化

上电之后的操作:

step1:200us的延时(DQM和CKE需要拉高)

step2:预充电命令

step3:8次自动刷新命令(也可以在step4之后完成)

step4:配置模式寄存器命令

三、自动刷新和自刷新

(1) SDRAM是动态内存,需要不断刷新才能保存数据,存储体中的电容需要不断地刷新才能不会因为电容的自消耗而产生电位变化

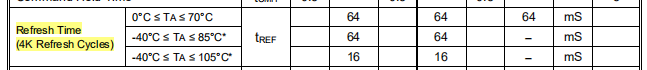

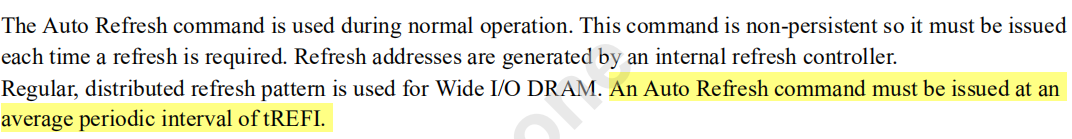

SDRAM的电容刷新时间是64ms

在64ms内需要4K个自动刷新

(2) 芯片手册未找到自动刷新与自刷新的详细解释,所以参考了另外一篇博客

https://www.cnblogs.com/tureno/articles/6085741.html

自动刷新(Auto Refresh,简称AR)与自刷新(Self Refresh,简称SR)。不论是何种刷新方式,都不需要外部提供行地址信息,因为这是一个内部的自动操作。

对于AR, SDRAM内部有一个行地址生成器(也称刷新计数器)用来自动的依次生成行地址。由于刷新是针对一行中的所有存储体进行,所以无需列寻址,或者说CAS在RAS之前有效。所以,AR又称CBR(CAS Before RAS,列提前于行定位)式刷新。由于刷新涉及到所有L-Bank,因此在刷新过程中,所有L-Bank都停止工作,而每次刷新所占用的时间为9个时钟周期(PC133标准),之后就可进入正常的工作状态,也就是说在这9 个时钟期间内,所有工作指令只能等待而无法执行。64ms之后则再次对同一行进行刷新,如此周而复始进行循环刷新。显然,刷新操作肯定会对SDRAM的性能造成影响,但这是没办法的事情,也是DRAM相对于SRAM(静态内存,无需刷新仍能保留数据)取得成本优势的同时所付出的代价。

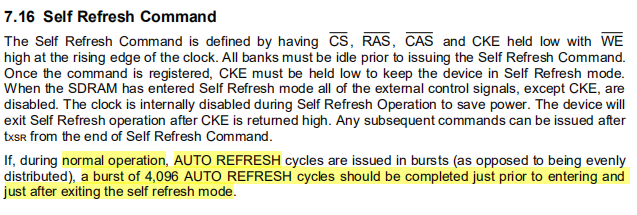

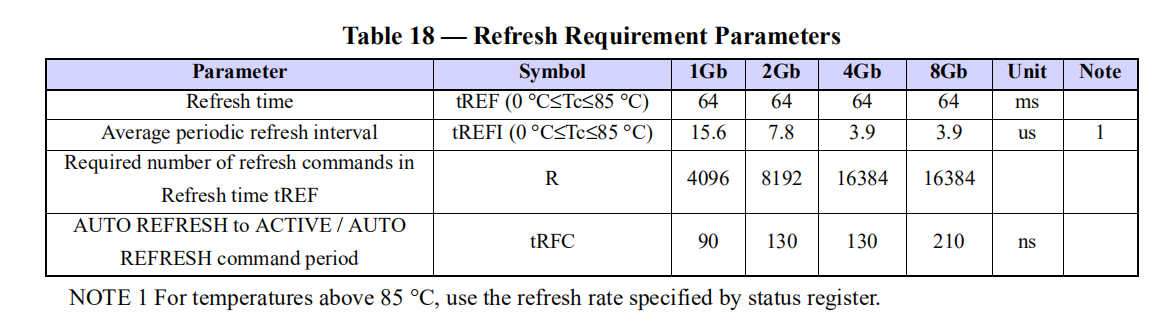

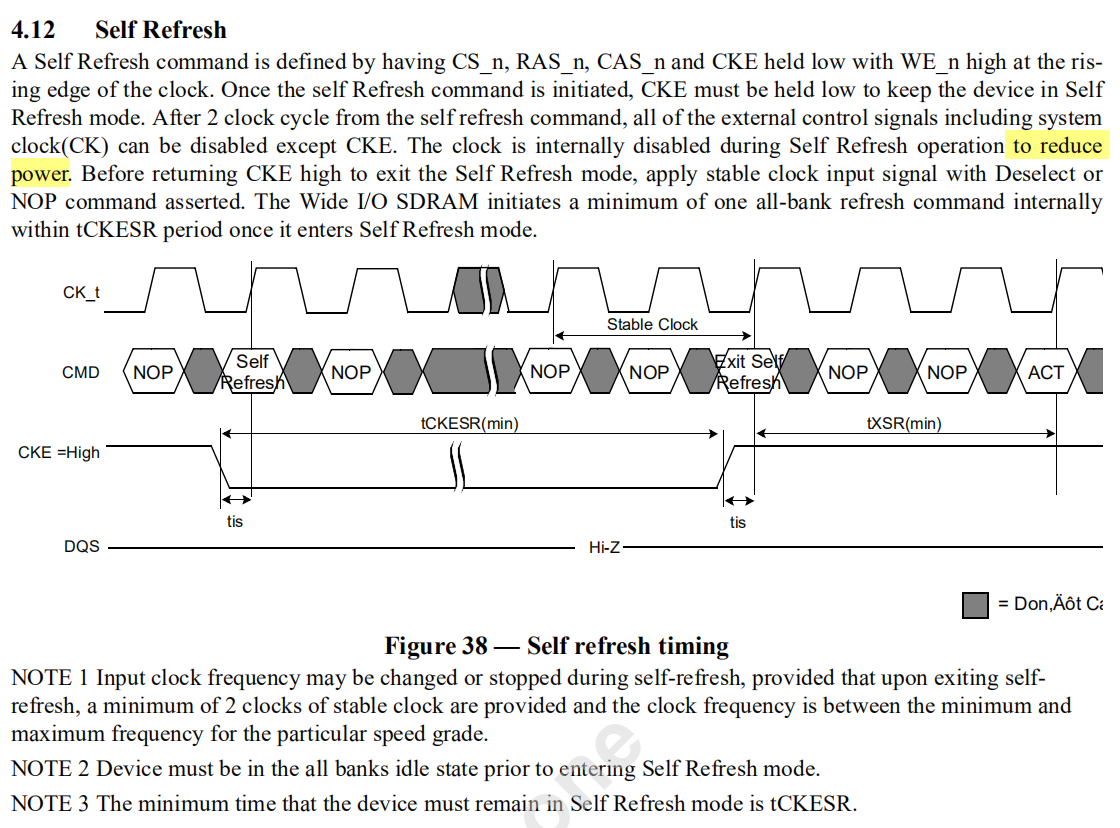

SR则主要用于休眠模式低功耗状态下的数据保存,这方面最著名的应用就是STR(Suspend to RAM,休眠挂起于内存)。在发出AR命令时,将CKE置于无效状态,就进入了SR模式,此时不再依靠系统时钟工作,而是根据内部的时钟进行刷新操作。在SR期间除了CKE之外的所有外部信号都是无效的(无需外部提供刷新指令),只有重新使CKE有效才能退出自刷新模式并进入正常操作状态。

如果如果在SR模式中,是不可以发出AR命令的 (如果AR是突发的,要在SR命令退出之后或者进入之前发出)

每一次自动刷新只会刷新一行,而sdram有4K行,想要全部刷新完需要4K次,如果没有在规定时间内完成自动刷新就会导致sdram丢失数据

通过查找,JEDEC标准JESD229找到了关于刷新的解释

四、读写操作

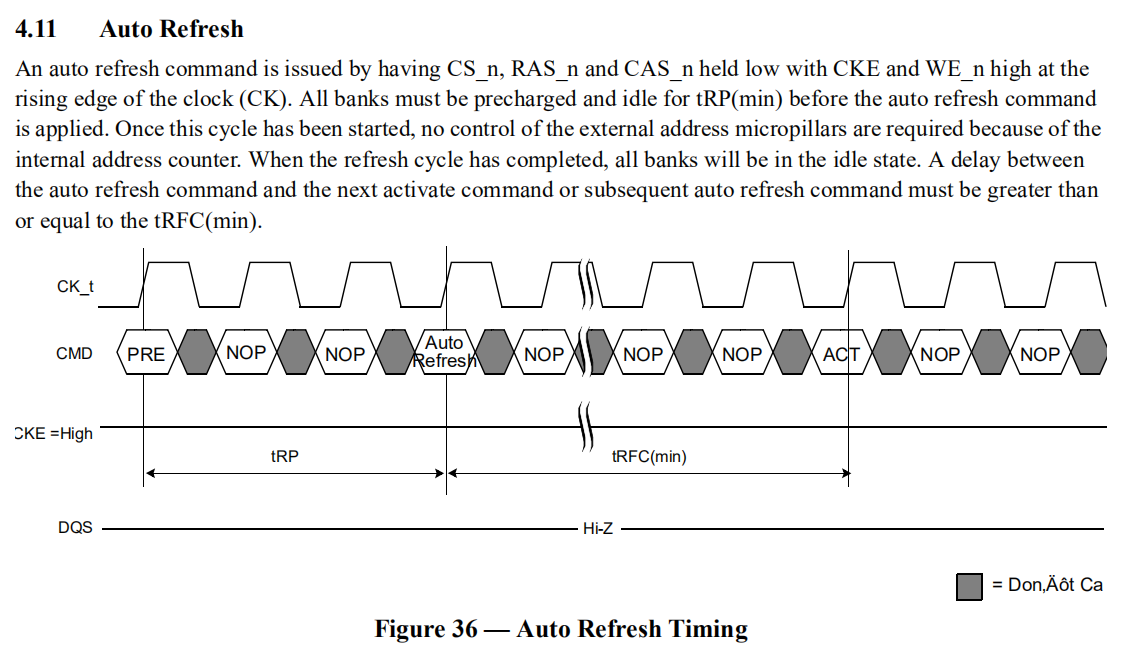

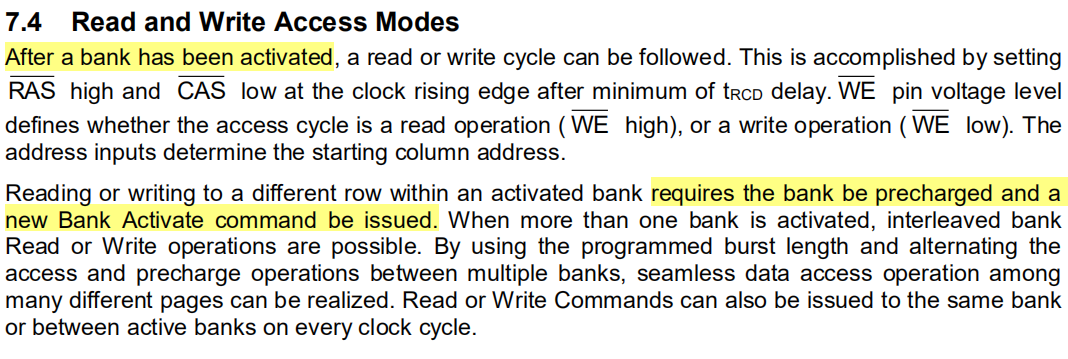

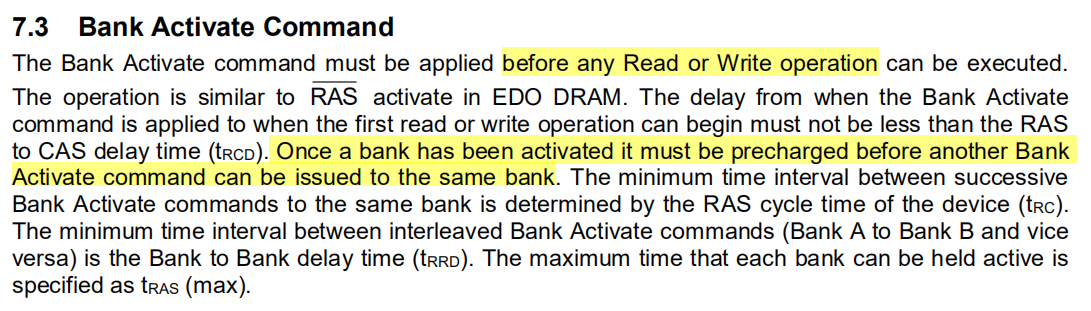

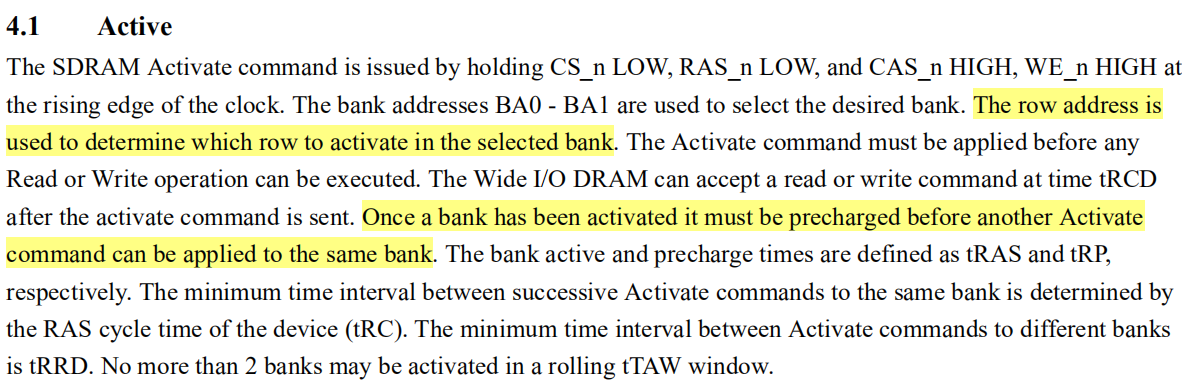

- 在读写操作之前,需要Active命令

- Active命令通过选择行地址,激活被选中BANK里的行,ACtive命令发出之前,需要有precharge命令

- Precharge命令是用来关闭BANK的

- 因此在读写操作时,需要先关闭所有BANK,然后激活选中BANK里的行,再读出或写入数据到列中

浙公网安备 33010602011771号

浙公网安备 33010602011771号