FPGA——vivado FIFO问题记录

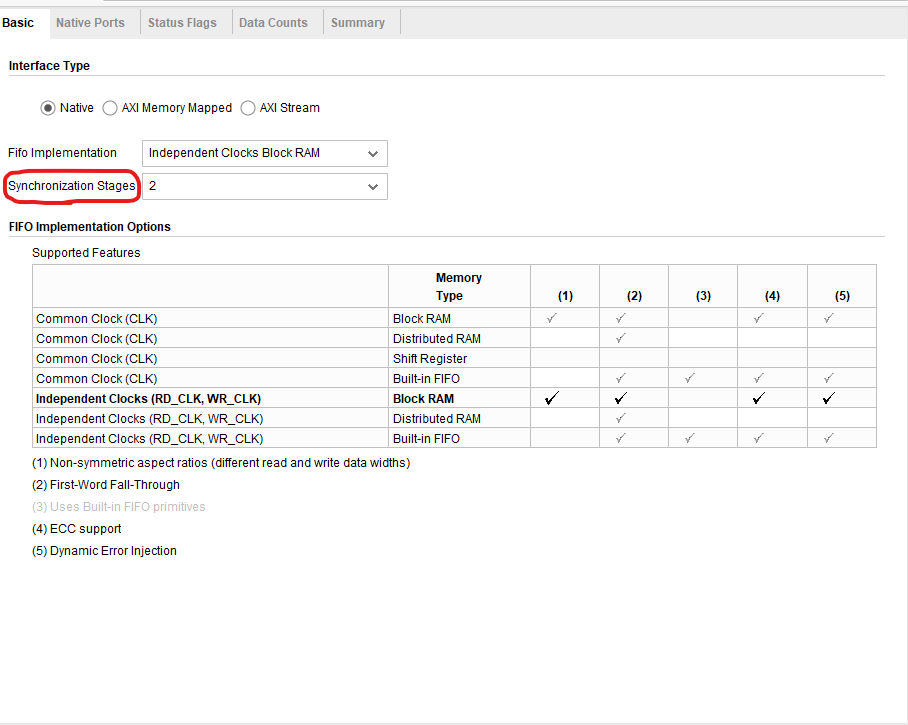

(1)标准FIFO下 synchronization stage

异步时钟FIFO独有的值

表示FIFO 读时钟域的 rd_data_out开始有值的时间

当 synchronization stages = 4时

在write_data_count被写入值后,经过(synchronization stages + 2) = 4个读时钟上升沿,read_data_count+1

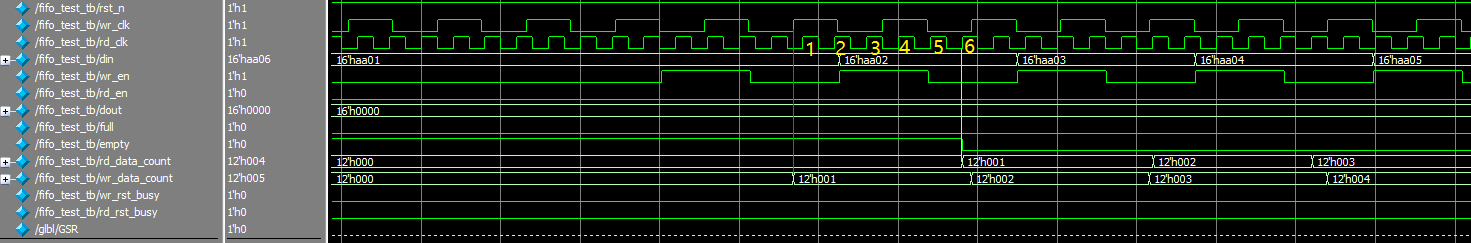

(2)wr_data_out

写时钟第一个上升沿检测到读使能,写入一个数据

写时钟第二个上升 wr_data_out + 1

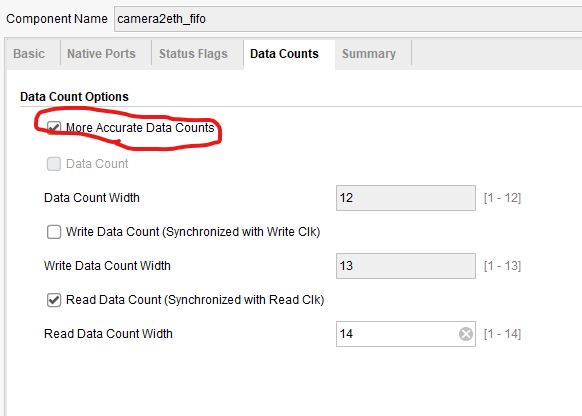

(3)more accurate data counts

在FIRST FIFO 要加上more accurate data counts

如果不加,rd_data_count,rd_data_count = 实际FIFO内数据个数 - 2

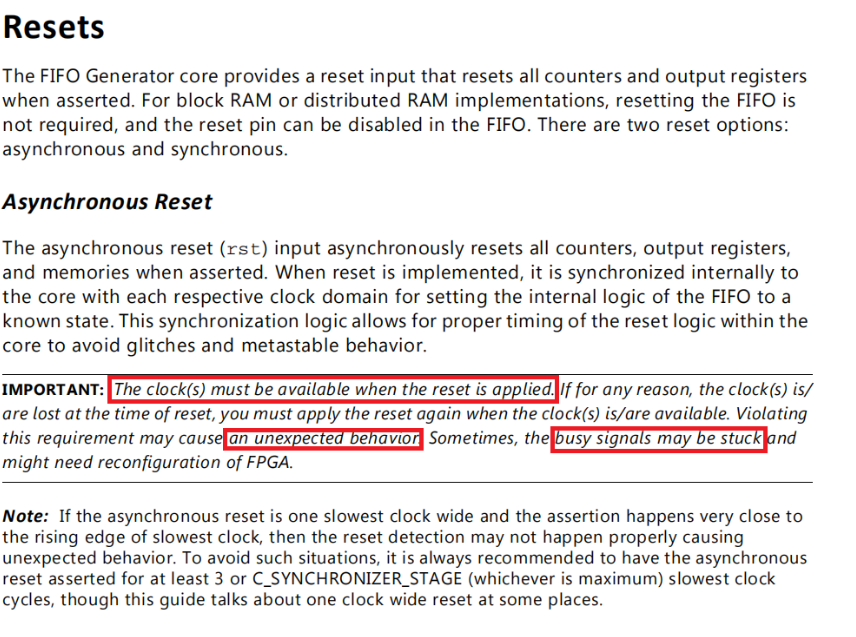

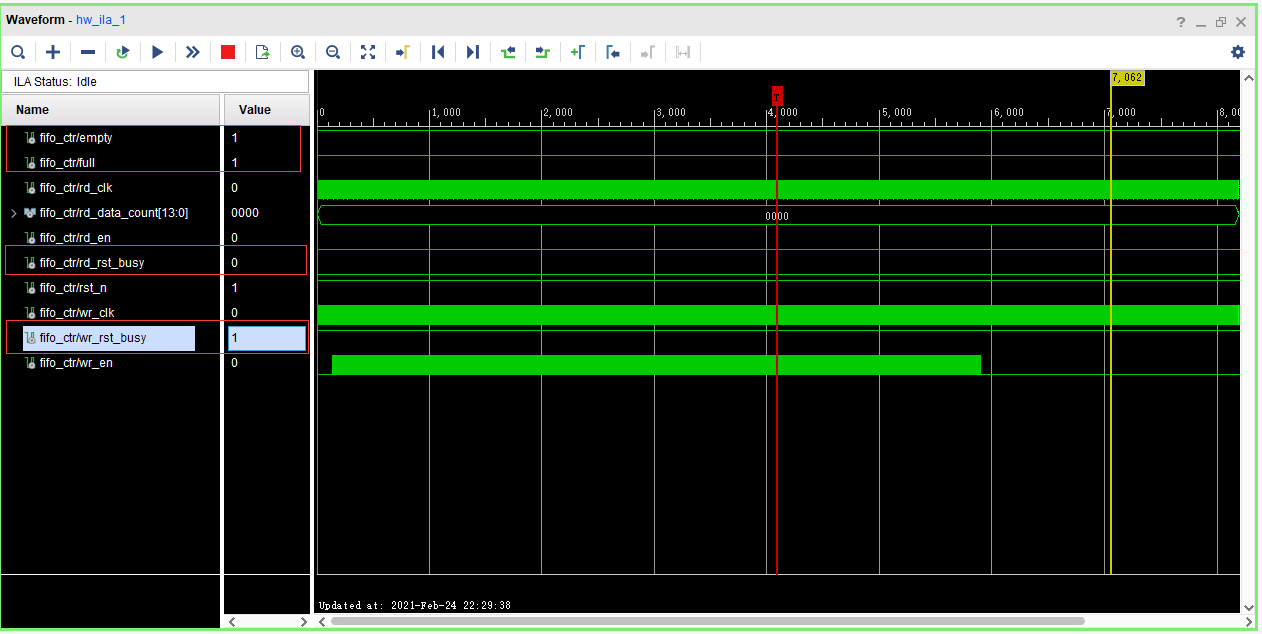

(4)FIFO复位后写不进去的问题

复位时,时钟要存在,不存在busy信号就会跑飞

复位时,写时钟消失

复位后,busy信号拉高,FIFO跑飞,不能写入数据

解决办法:

1、让时钟在复位时,也能工作

2、如果不能让时钟在复位时工作,那么就不能使用busy信号,分别设置wr_rst和rd_rst

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· AI与.NET技术实操系列:基于图像分类模型对图像进行分类

· go语言实现终端里的倒计时

· 如何编写易于单元测试的代码

· 10年+ .NET Coder 心语,封装的思维:从隐藏、稳定开始理解其本质意义

· .NET Core 中如何实现缓存的预热?

· 25岁的心里话

· 闲置电脑爆改个人服务器(超详细) #公网映射 #Vmware虚拟网络编辑器

· 基于 Docker 搭建 FRP 内网穿透开源项目(很简单哒)

· 零经验选手,Compose 一天开发一款小游戏!

· 一起来玩mcp_server_sqlite,让AI帮你做增删改查!!