vivado警告记录——[Timing 38-316]

警告记录:[Timing 38-316] Clock period '20.000' specified during out-of-context synthesis of instance 'dds_module/dds_rom' at clock pin 'clka' is different from the actual clock period '8.000', this can lead to different synthesis results.

意思:vivado的ROM ip的20ns时钟约束与实际时钟8ns不符

这个警告来源于vivado rom ip自带的ooc.xdc约束文件,该警告不会影响implement,因此可以忽略

但是想去除这个警告也是有办法的

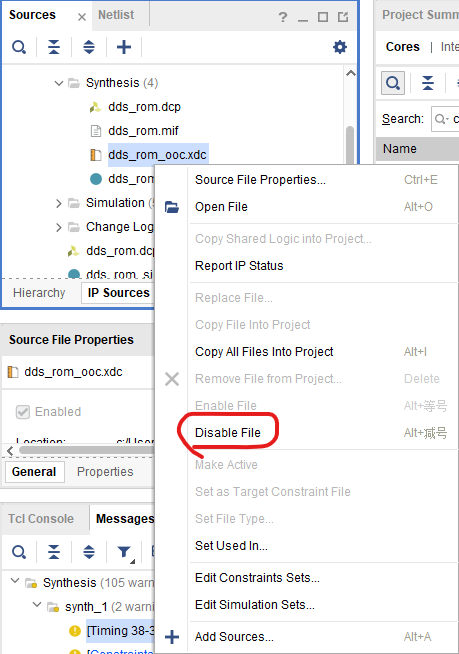

方法:

禁用自带的约束文件

https://forums.xilinx.com/t5/Vivado/基于IPcore的RAM综合时警告-Timing-38-316-Clock-period-20-000-specified/m-p/1122201

浙公网安备 33010602011771号

浙公网安备 33010602011771号