亚稳态时序图图解

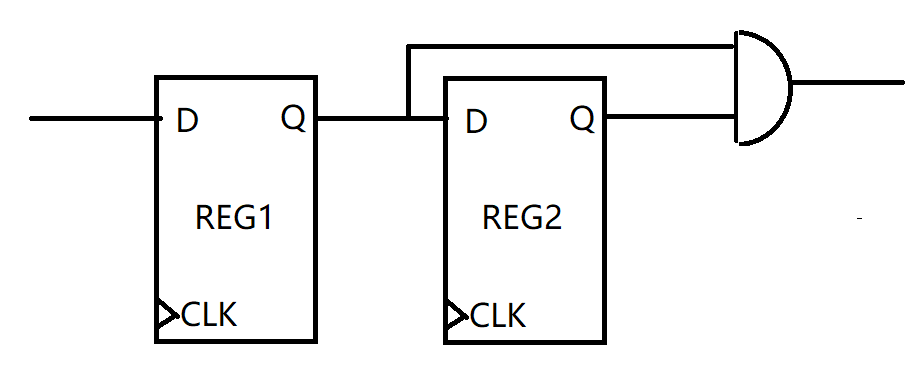

一、异步信号边缘检测,接两级D触发器,防止亚稳态

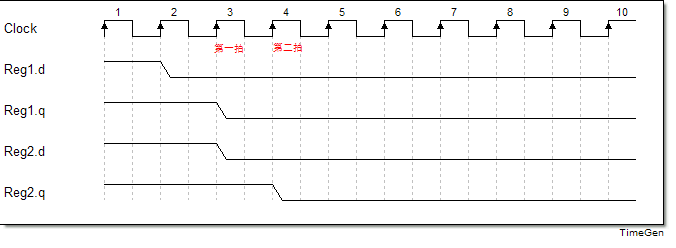

二、没有亚稳态的时序图

在第二拍就可以检测到下降沿

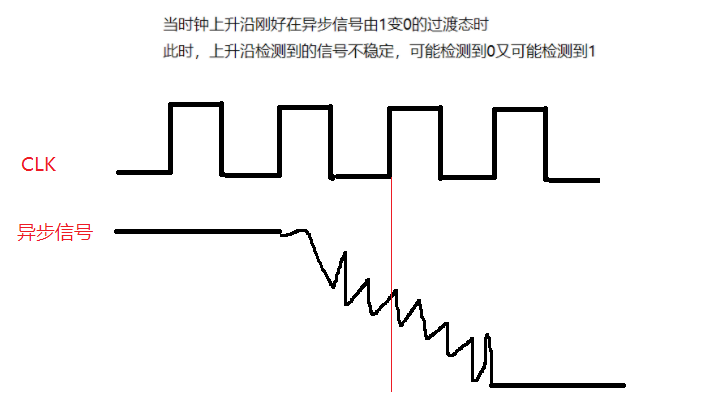

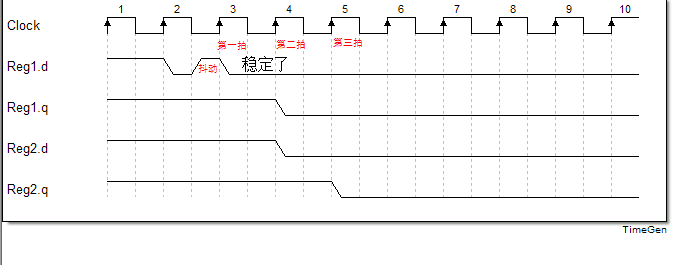

三、有亚稳态的时序图,以及为什么二级触发器就能防止亚稳态

在第一拍到来之前,出现抖动,原本是0,现在变成了1

要慢一拍,在第三个时钟上升沿,检测到下降沿

四、verilog代码构建二级触发器,解决亚稳态方案

写法1

1 reg[2:0] uart_sync; 2 always @(posedge clk or negedge rst_n)begin 3 if(!rst_n)begin 4 uart_sync <= 3'b111; 5 end 6 else 7 uart_sync <= {uart_sync[1:0],rx_uart}; 8 end 9 //下降沿检测 10 assign nedge = uart_sync[2:1] == 2'b10; 11 //上升沿检测 12 assign pedge = uart_sync[2:1] == 2'b01;

写法2

1 reg[2:0] uart_sync; 2 always @(posedge clk or negedge rst_n)begin 3 if(!rst_n)begin 4 uart_sync <= 3'b111; 5 end 6 else begin 7 uart_sync[0] <= rx_uart; 8 uart_sync[1] <= uart_sync[0]; 9 uart_sync[2] <= uart_sync[1]; 10 end 11 end 12 assign nedge = uart_sync[2] && !uart_sync[1]; 13 assign pedge = !uart_sync[2] && rx_uart_sync[1];