2018-2019-1 20165228 《信息安全系统设计基础》第四周学习总结

2018-2019-1 20165228 《信息安全系统设计基础》第四周学习总结

教材学习内容总结

Y86-64指令集体系结构

Y86程序中的每条指令都会读取或修改处理器状态的某些部分

程序员可见状态

-

15个程序寄存器(RF):每个寄存器存储一个64位,即8字节的字(即Y86-64指令长度)

-

3个条件码(CC):ZF(零标志位)/SF(符号标志位)/OF(溢出标志位)

-

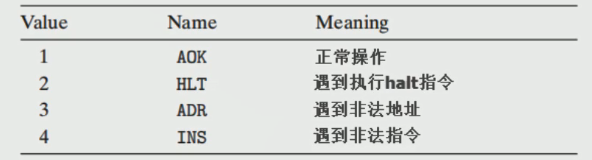

程序状态(Stat)

![]()

-

程序计数器(PC):存放当前正在执行指令的地址,计算下一条指令的地址时,根据当前指令的编码长度计算。

-

内存(DMEM):很大的字节数组,用来存放程序和数据。

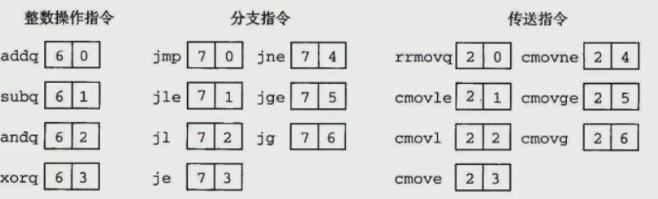

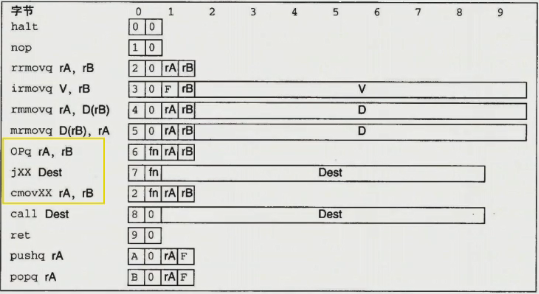

Y86-64指令

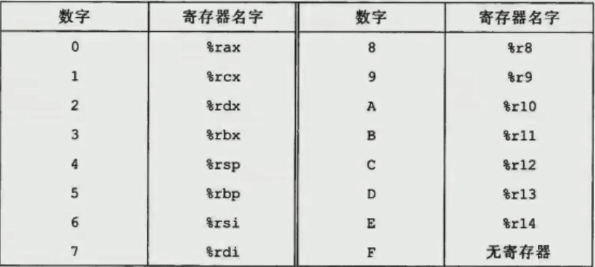

Y86-64程序寄存器标识符:

- 寄存器标识符范围:0-0xE

- 程序寄存器的存储:寄存器文件

- 不应访问任何寄存器:用0xF表示

![]()

Y86-64指令编码 - 编码长度:1字节~10字节

- 组成:1、一个单字节的指令指示符

2、一个单字节的寄存器指示符

3、一个八字节的常数字

各指令详细解释: - halt指令:十六进制表示为00,占一个字节。执行时,使处理器停止。

- nop指令:十六进制表示为10,占一个字节。

- rrmovq rA,rB指令:十六进制表示为 20 rArB,占两个字节。

- ...

![]()

Y86-64指令集的功能码:高四位为代码部分,低四位为功能部分。

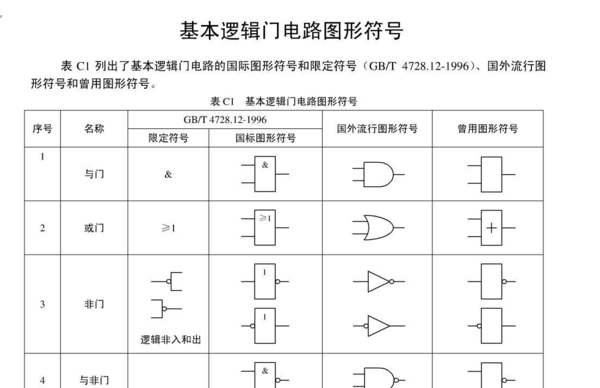

逻辑设计和硬件控制语言HCL

为实现一个数字系统需要三个重要的组成部分:

-

计算对位进行操作的函数的组合逻辑

-

存储位的存储单元

-

控制存储单元更新的时钟信号

HCL与HDL的区分 -

HCL:硬件控制语言

-

HDL:硬件描述语言

HCL表达式中的运算符:都只对单个字进行操作 -

与:AND用“&&”表示

-

或:OR用“||”表示

-

非:NOT用“!”表示

-

与、或、非三种逻辑门可以用一种与非门或者或非门实现

![]()

组合电路:多个逻辑门组合成网(必须无环)构成计算块,称为组合电路。 -

多个逻辑门组合时的限制:每个逻辑门的输入必须连接到下述选项之一,且两个或多个逻辑门的输出不能连接在一起。

1、一个系统输入

2、某个存储器单元的输出

3、某个逻辑门的输出

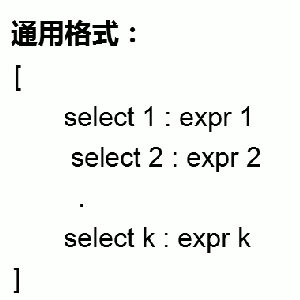

HCL整数表达式 -

情况表达式:

![]()

-

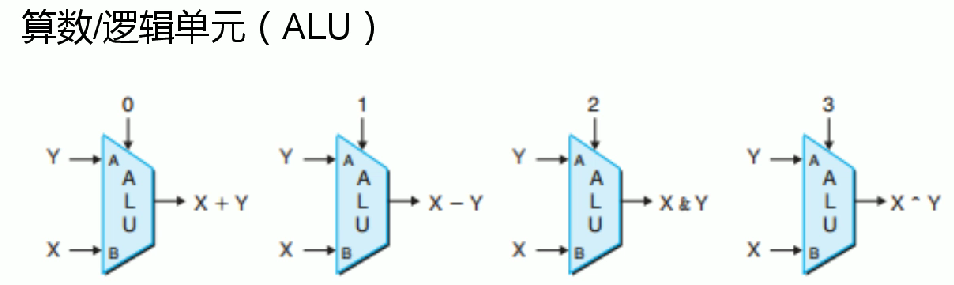

算数/逻辑单元(ALU):加、减、与、异或

![]()

-

集合关系:

iexpr为被测试的值,iexpr1~iexprk为带匹配的值,均为正数表达式。

iexpr in { iexpr1,iexpr2,...,iexprk }

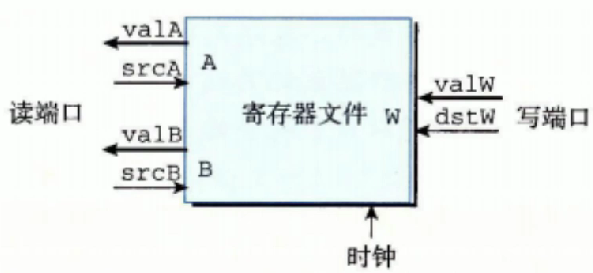

存储器和时钟

按位存储信息的设备

- 时钟寄存器:简称寄存器,存储单个位或字。Y86-64中使用是中寄存器保存程序计数器PC、条件代码CC和程序状态Stat

- 随机访问寄存器:简称内存,存储多个字。

寄存器 - 硬件寄存器:将其输入和输出的线连接到电路的其他部分。当时钟上升沿到来才会加载新的输入信号并输出,是电路不通部分中组合逻辑之间的屏障。

- 程序寄存器:CPU中为数不多的可寻址的字,这里的地址为寄存器ID,这些字通常都存在寄存器文件中。

寄存器组成:两个读端口、一个写端口、时钟

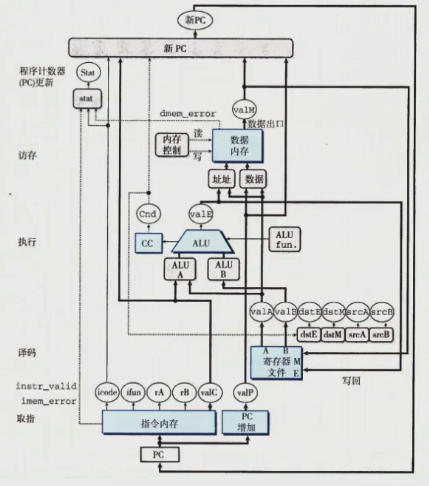

Y86-64的顺序实现

将处理器组织成阶段

- 六阶段

1、取值:fetch

2、译码:decode

3、执行:execute

4、访存:memory

5、写回:write back

6、更新:PC update - SEQ硬件结构:

![]()

SEQ的实现

- 两种存储器设备

1、时钟寄存器(程序计数器和条件码寄存器)

2、随机访问寄存器(寄存器文件、指令内存和数据内存)

时序控制 - 程序计数器

- 条件码计数器

- 数据内存

- 寄存器文件

浙公网安备 33010602011771号

浙公网安备 33010602011771号