ZYNQ的C裸机应用编程学习

刚看ZYNQ这边的裸机编程,也就是逻辑单元与ARM之间开始协作作业。需要用到SDK,但是vivado19之后,sdk已经换成vitis,功能一样,使用稍微变化。

第一次使用,按照小梅哥点灯的程序运行就出现了问题。有时候vitis下载run进去能亮,有时候亮不起来。

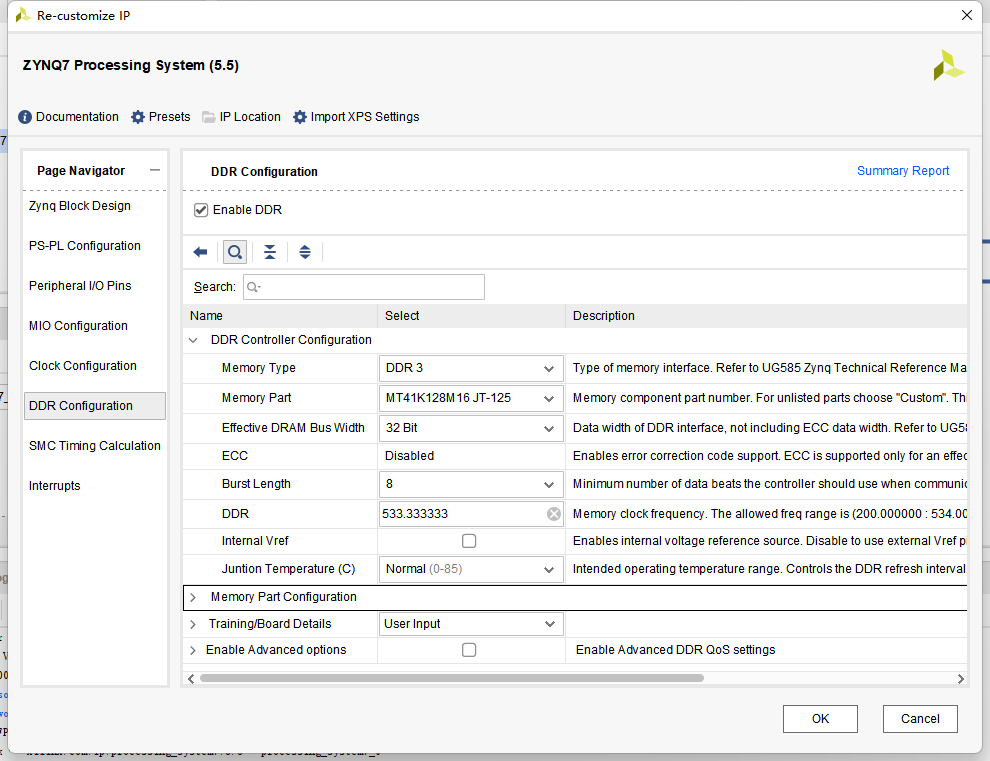

最后发现,是在创建PS应用的时候,这边zynq的DDR3的芯片选择出了问题,是128M16位,选择了8位(MT41K256M16XX-125)。

但是为什么有时候能亮,虽然频率很低,但是我也好奇,这个只能进行深入的学习,才能了解。

粗心问题,下次对于硬件的选型问题,需要仔细一点。不然代码写再多都是白费。

ZYNQ的GPIO介绍

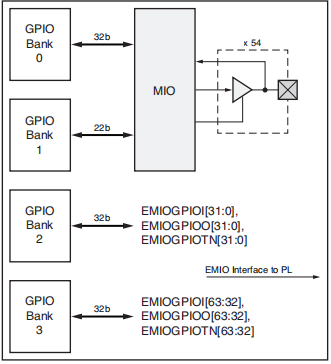

MIO(multiuse I/O):多功能IO接口,属于Zynq的PS部分,Zynq7000 系列芯片有 54 个 MIO。它们分配在 GPIO 的 Bank0 和 Bank1 上,这些引脚可以用在GPIO、SPI、UART、TIMER、Ethernet、USB等功能上,每个引脚都同时具有多种功能,故叫多功能IO接口。这些 IO 与 PS 直接相连。不需要添加引脚约束,MIO 信号对 PL部分是透明的,不可见。所以对 MIO 的操作可以看作是纯 PS 的操作。GPIO 的控制和状态寄存器基地址为:0xE000_A000,我们 SDK 下软件操作底层都是对于内存地址空间的操作。

EMIO(extendable multiuse I/O):扩展MIO,依然属于Zynq的PS部分,只是连接到了PL上,再从PL的引脚连到芯片外面实现数据输入输出。Zynq7000 系列芯片有 64 个 EMIO,它们分配在 GPIO 的 Bank2 和 Bank3 上,当 MIO 不够用时,PS 可以通过驱动 EMIO 控制 PL 部分的引脚,EMIO 的使用相当于,是一个 PS + PL 的结合使用的例子。所以,EMIO 需要分配引脚以及编译综合生成 bit文件。

AXI_GPIO相当于GPIO的IP核,是通过AXI总线挂在PS上的GPIO上。

ZYNQ的GPIO由4个BANK组成,其体系结构如图1所示。其中Bank0有32个GPIO引脚,Bank1有22个引脚,共54个GPIO引脚直接通过MIO连接到PS上,每个引脚可以通过寄存器的设置来确定该引脚为输入、输出或者中断,因为54个MIO引脚直接连接在PS上,像其他普通ARM一样,不需要通过XPS进行硬件配置,直接通过SDK编程即可。

Bank2和Bank3通过EMIO接口将CPU的GPIO连接到PL部分的引脚上,其中每个Bank各有32个引脚,通过EMIO扩展的GPIO连接到PL上,可以在PL部分进行逻辑设计,进行特定功能的IP核制定。然后在PS部分,像控制普通MIO一样进行编程。因此,使用EMIO引脚必须通过XPS进行硬件配置,然后在PS部分使用SDK进行编程控制。

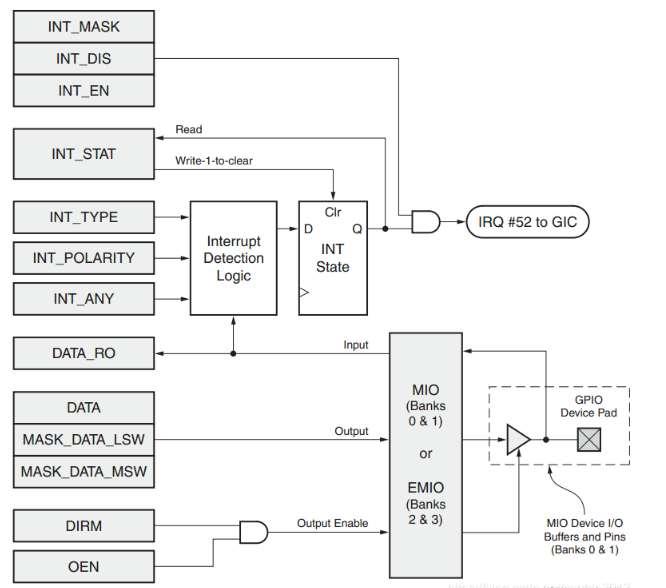

DATA_RO: 读取GPIO引脚值寄存器,不论该GPIO引脚配置为输入还是输出,都能正确读取该GPIO引脚值。如果该引脚的功能没有配置成GPIO功能,读取的值为随机值,因为该寄存器只能读取GPIO引脚值。。

DATA: 此寄存器控制输出到 GPIO 的值,读这个寄存器的值可以读到最后一次写入该寄存器的值。

MASK_DATA_LSW: 位操作寄存器,写入 GPIO 低 16bit 其他没有改变的位置保存原先的状态

MASK_DATA_MSW: 位操作寄存器,写入 GPIO 高 16bit 其他没有改变的位置保存原先的状态

DIRM: 此寄存器控制输出的开关,当 DIRM[x]==0 时候,禁止输出

OEN: 输出使能,当 OEN[x]==0 的时候输出关闭,PIN 脚处于三态。因此,如果要读 IO 状态就得读 DATA_RO 的值,如果是对某一位进行操作就是写MASK_DATA_LSW/MASK_DATA_MSW

本文来自博客园,作者:祈愿树下,转载请注明原文链接:https://www.cnblogs.com/cjl520/p/18102039