startRC使用记录

startRC的使用前提:

PR阶段已经输出相应的verilog、gds

ICC命令:

write_verilog -macro_definition -no_physical_only_cells ./filename/verilog_name.v

-macro_definition为软宏编写模块定义。软宏是在设计规划期间生成的用户分区宏。大多数大型设计都倾向于划分为几个分区的宏。当您使用这个选项时,Verilog编写器会查看软宏内部并写出内部细节。单元格的全部内容也会被写入。默认情况下,软宏被视为叶宏,不会写入其定义。

-no_physical_only_cells防止只写入物理单元实例。这个选项等价于同时使用-no_pg pin_only_cells和-no_core_filler_cells选项。

write_stream -lib_name -format gds -cells

write_stream将设计(库)写入GDSIII或Oasis文件。

-lib_name lib_name指定包含布局单元格的库名称。如果未指定,则使用当前打开的库。

-format GDS |绿洲输出文件的格式。取值必须为gds或oasis。默认格式为gds。

单元文件cell_name_file指定包含要输出的单元格名称的文件的名称。此选项仅适用于GDS。

startRC的环境配置

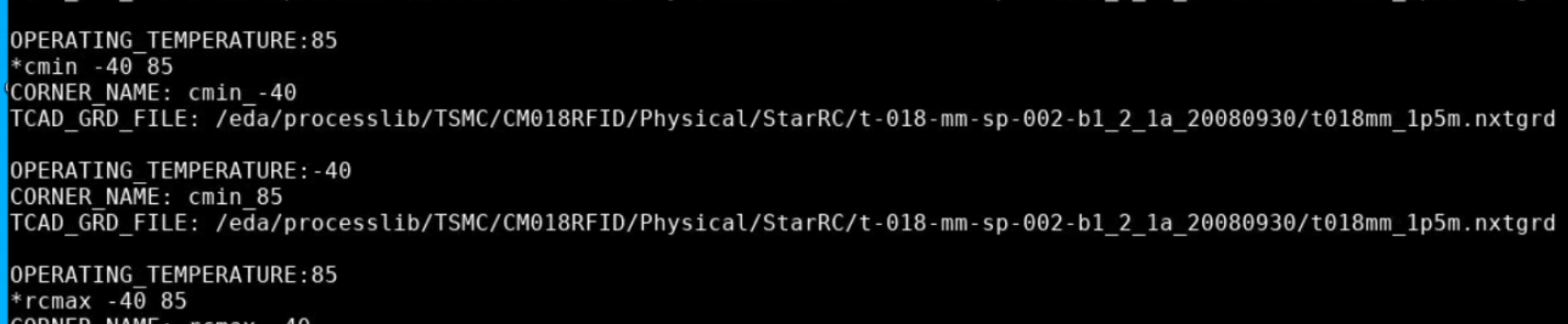

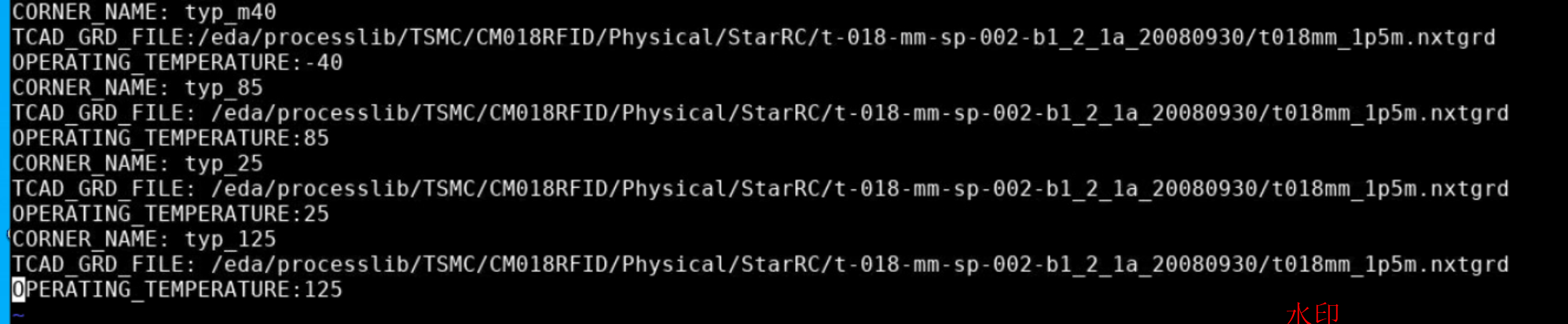

corners_file

文件中包括Corner_name、Corner_name相对应的TCAD_GRD_FILE(.nxtgrd)、温度

corners_list

文件中是自己需要使用的corner,这部分corner的配置同corner_file

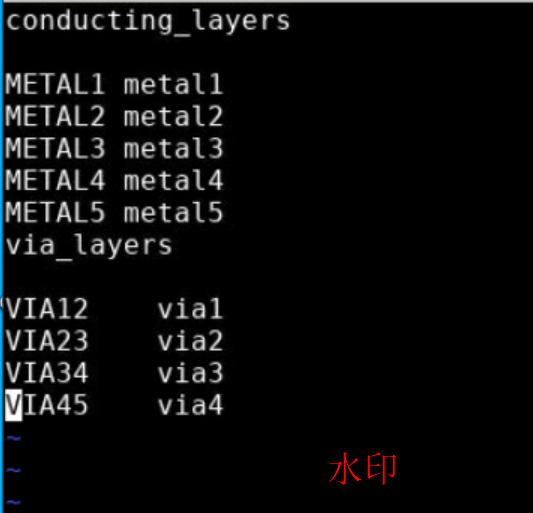

star.map

文件中包含用到的metal和via

star_cmd

ICC环境下的common文件配置

BLOCK指MIKYWAY下对应存储数据的mw_cell

ICC2环境同理

43行的power net是指当前design中的电源走线,在starrc中是需要移除的,选择对应的net name输入,使其移除

浙公网安备 33010602011771号

浙公网安备 33010602011771号