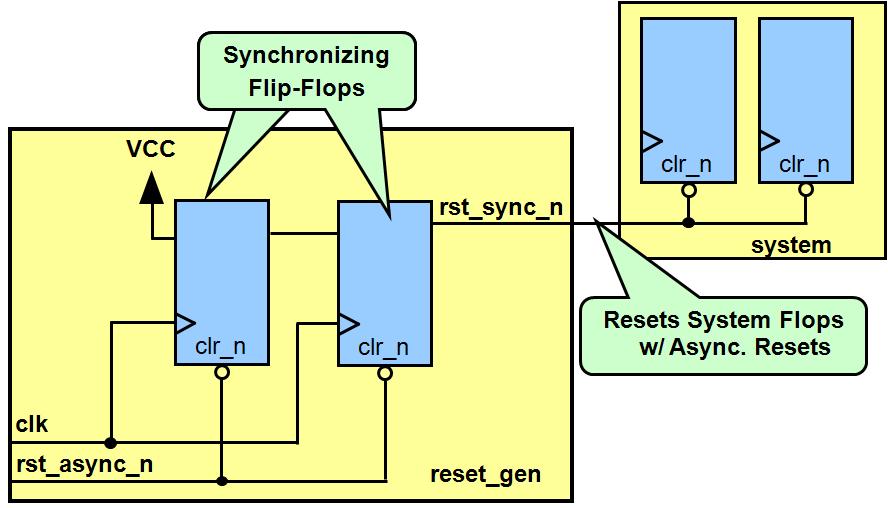

什么是异步复位同步释放

1.电路原理图

2.verilog代码描述

module reset_gen ( output rst_sync_n, input clk, rst_async_n); reg rst_s1, rst_s2; wire rst_sync_n ; always @ (posedge clk, posedge rst_async_n) if (rst_async_n) begin rst_s1 <= 1'b0; rst_s2 <= 1'b0; end else begin rst_s1 <= 1'b1; rst_s2 <= rst_s1; end assign rst_sync_n = rst_s2; //注意这里的rst_sync_n才是我们真正对系统输出的复位信号 endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号