音频IIS并转串仿真---verilog

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: chensimin // // Create Date: 2018/06/11 11:07:55 // Design Name: // Module Name: iis_p2s // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module iis_p2s( input wire Aud_rst, input wire Aud_clk, output reg Aud_data_in_req, output wire ws_pulse, output reg Aud_sck, // 3.072M audio clock output reg Aud_ws, // 48k output reg [0:0] Aud_sd ); reg [0:0]Aud_sd = 0; wire [23:0]Aud_data_l; assign Aud_data_l = 24'hAAAAAB; wire [23:0]Aud_data_r; assign Aud_data_r = 24'hAAAAAB; //--------------------------------------------------------------- reg [7 :0]audio_clock_counter = 0 ; always @ (posedge Aud_clk or posedge Aud_rst) begin if (Aud_rst) audio_clock_counter <= 8'b0 ; else audio_clock_counter <= audio_clock_counter + 1'b1 ; end //--------------------------------------------------------------- //将主时钟进行4分频 reg Aud_sck = 0; always @ (posedge Aud_clk or posedge Aud_rst) begin if (Aud_rst) Aud_sck <= 1'b0; else if(audio_clock_counter[0] == 1'b1) Aud_sck <= ~Aud_sck ; // 12.288M/4=3.072MHZ end //--------------------------------------------------------------- reg Aud_ws = 0; wire [6:0]chen_1; always @ (posedge Aud_clk or posedge Aud_rst) begin if (Aud_rst) Aud_ws <= 1'b0; else if(audio_clock_counter[6:0] == 8'h7f) Aud_ws <= ~Aud_ws ; // 12.288M/256 = 48KHz = fs = Aud_sck / 64 (64 < 128) end assign chen_1 = audio_clock_counter[6:0]; //--------------------------------------------------------------- reg audio_sck_delay = 0 ; always @ (posedge Aud_clk or posedge Aud_rst) begin if (Aud_rst) audio_sck_delay <= 1'b0; else audio_sck_delay <= Aud_sck; end //--------------------------------------------------------------- reg audio_ws_delay = 0 ; reg audio_ws_delay_d = 0; always @ (posedge Aud_clk or posedge Aud_rst) begin if (Aud_rst) begin audio_ws_delay <= 1'b0; audio_ws_delay_d <= 1'b0; end else begin audio_ws_delay <= Aud_ws; audio_ws_delay_d <= audio_ws_delay; end end wire sck_pulse_neg ; assign sck_pulse_neg = audio_sck_delay & ~Aud_sck ; assign ws_pulse = audio_ws_delay & ~Aud_ws ; //--------------------------------------------------------------- reg [23:0]audio_data_left_out = 0 ; reg [23:0]audio_data_right_out = 0; always @ (posedge Aud_clk or posedge Aud_rst) begin if (Aud_rst) begin audio_data_left_out <= 24'b0; audio_data_right_out <= 24'b0; end else if (sck_pulse_neg) begin if (ws_pulse) begin audio_data_right_out <= Aud_data_r ; audio_data_left_out <= Aud_data_l ; end else if (audio_ws_delay) audio_data_right_out <= {audio_data_right_out[22:0], 1'b0} ; else audio_data_left_out <= {audio_data_left_out[22:0], 1'b0} ; end end //--------------------------------------------------------------- always @ (posedge Aud_clk or posedge Aud_rst) begin if (Aud_rst) Aud_sd <= 1'b0; else if (sck_pulse_neg) begin if (audio_ws_delay) Aud_sd <= audio_data_right_out[23] ; else Aud_sd <= audio_data_left_out[23] ; end end //--------------------------------------------------------------- reg Aud_data_in_req = 0; always @ (posedge Aud_clk or posedge Aud_rst) begin if (Aud_rst) Aud_data_in_req <= 1'b0; else Aud_data_in_req <= ws_pulse ; end endmodule /* add_force {/iis_p2s/Aud_clk} -radix hex {1 0ns} {0 50000ps} -repeat_every 100000ps add_force {/iis_p2s/Aud_rst} -radix hex {1 0ns} {0 200ns} */

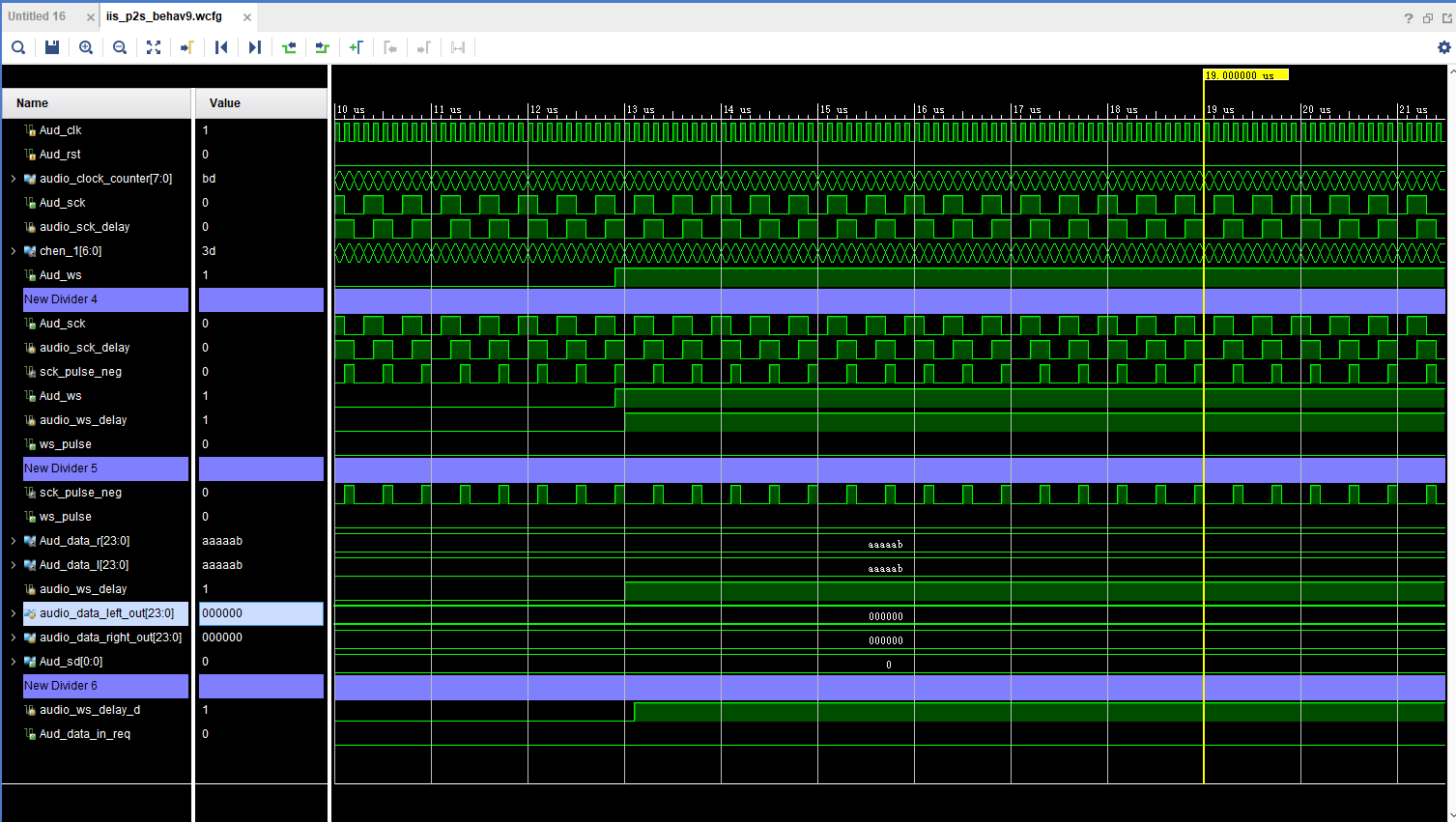

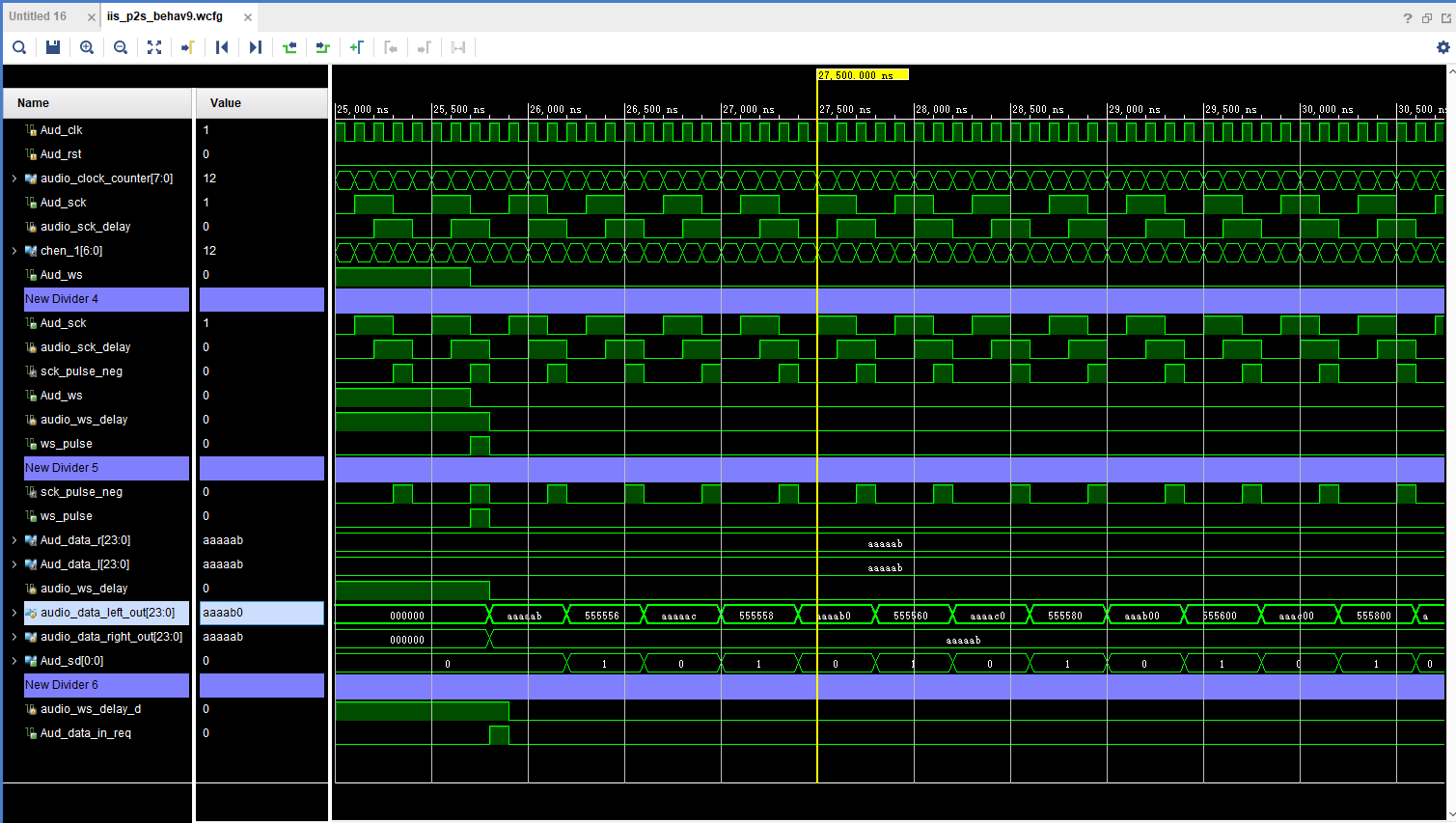

仿真结果: