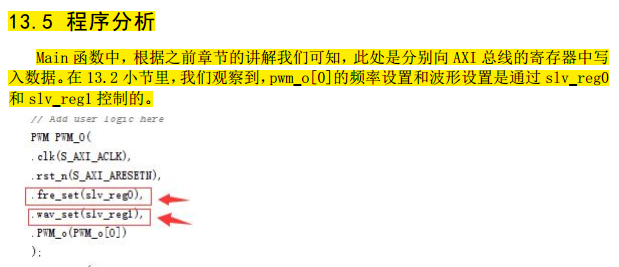

关于Xilinx AXI Lite 源代码分析---自建带AXI接口的IP

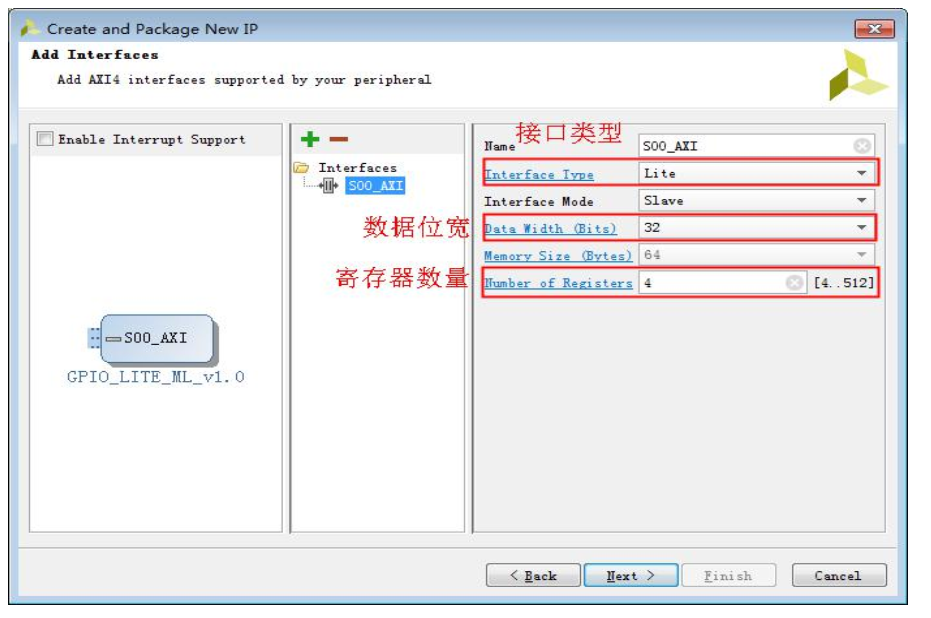

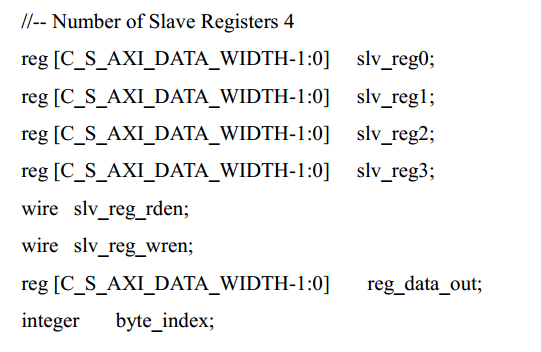

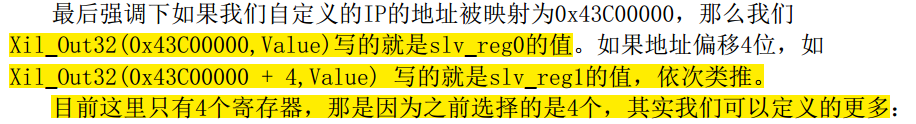

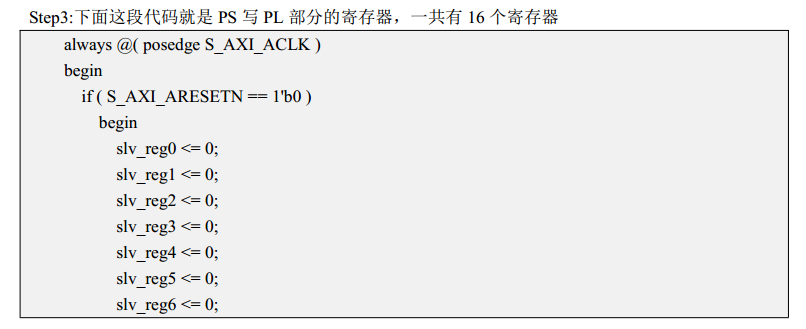

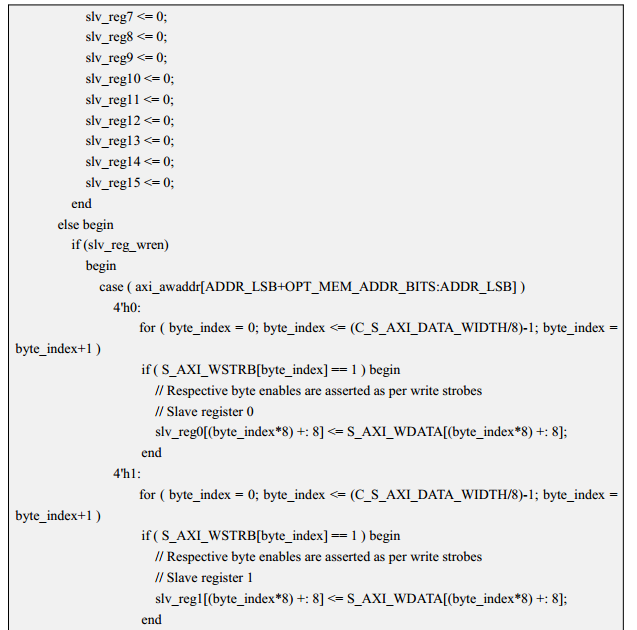

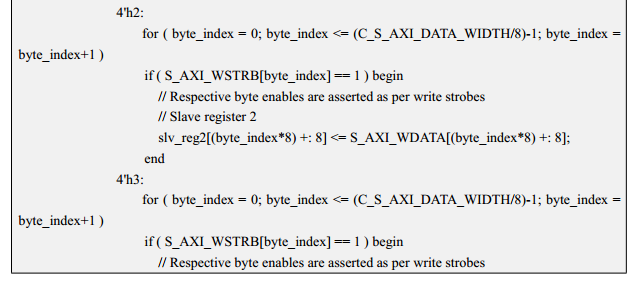

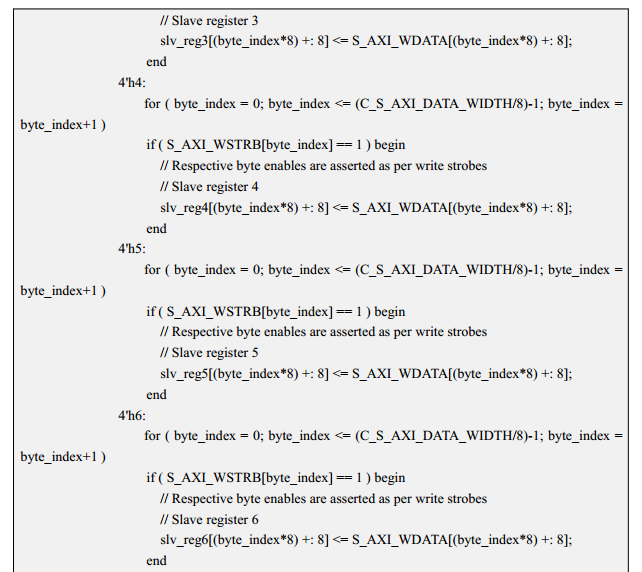

首先需要注意此处寄存器数量的配置,它决定了slv_reg的个数。

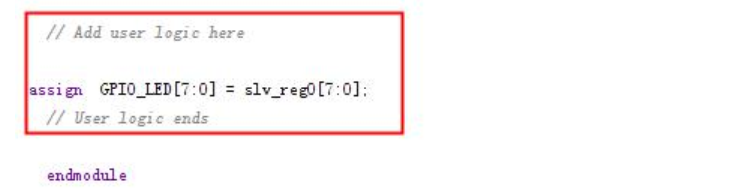

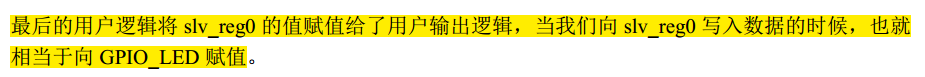

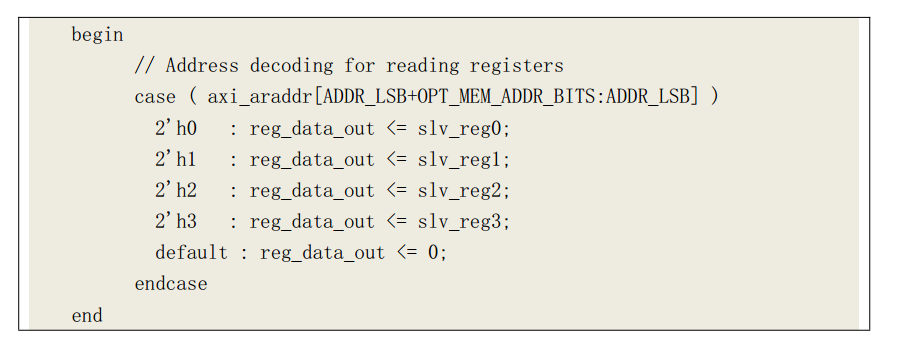

读写数据,即是对寄存器slv_reg进行操作:

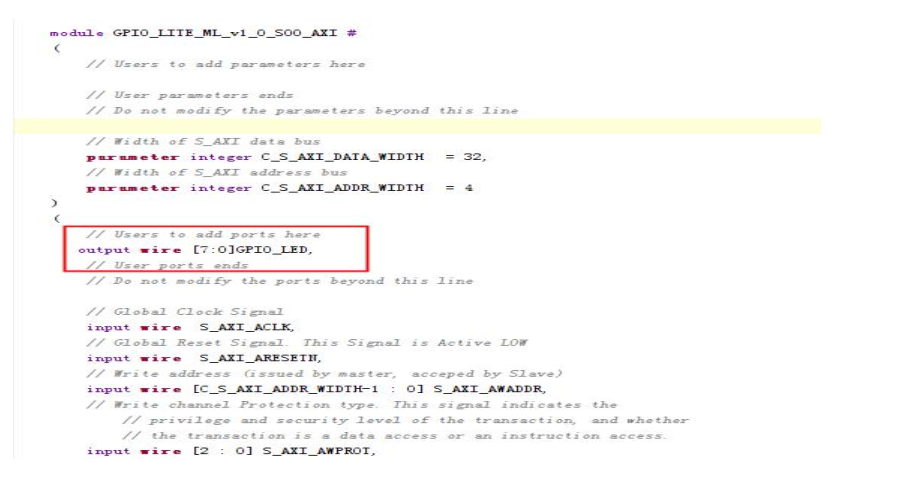

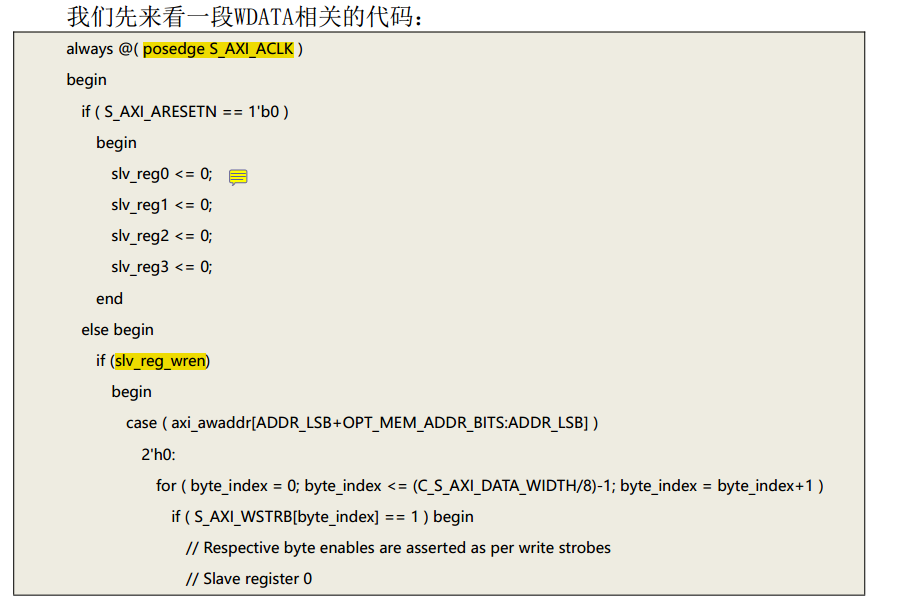

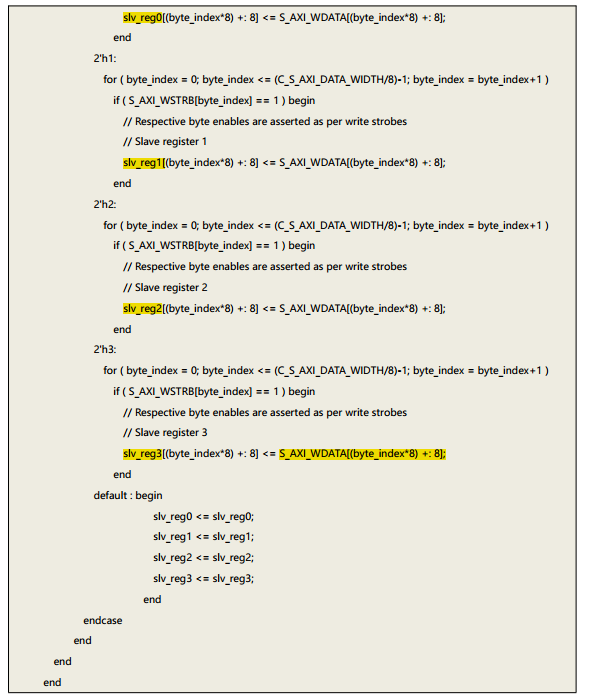

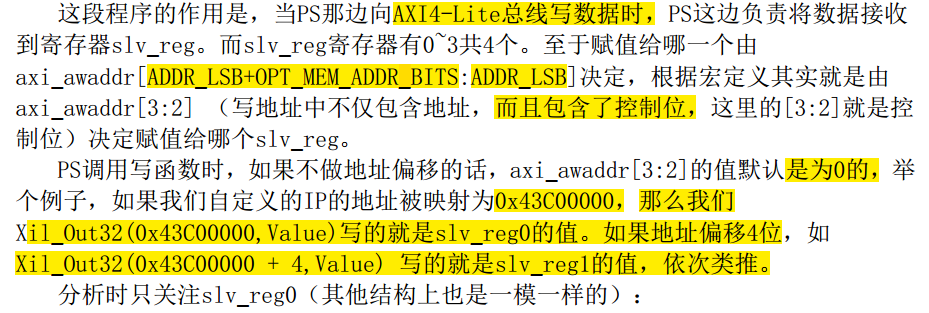

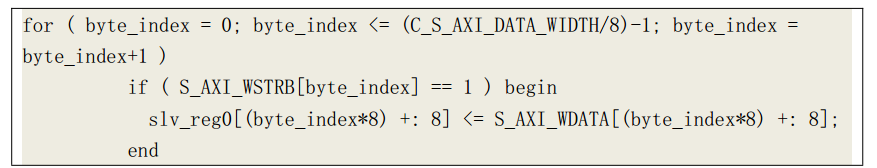

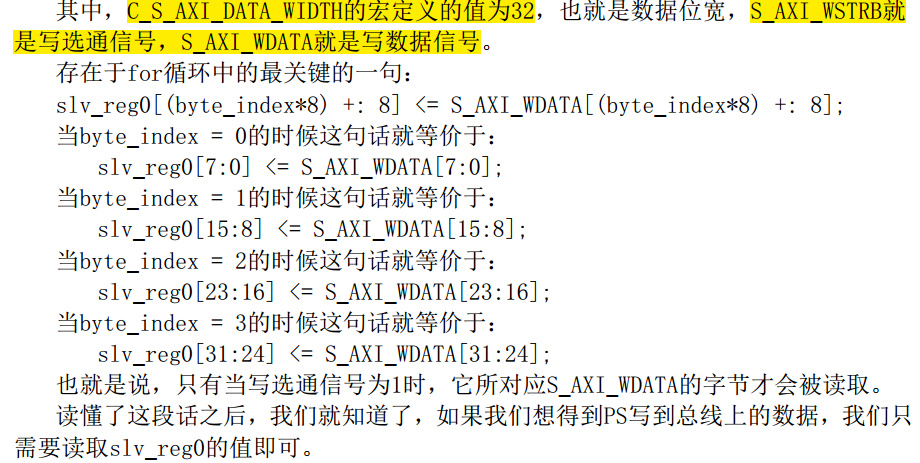

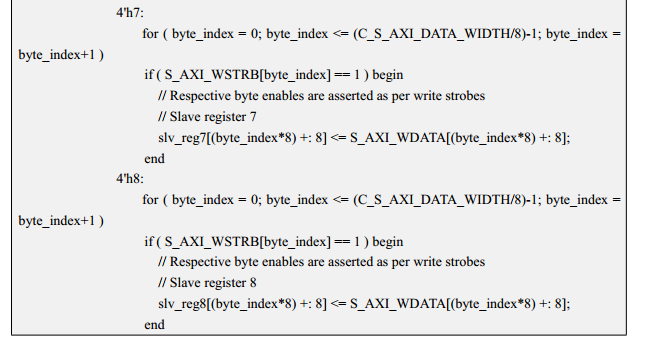

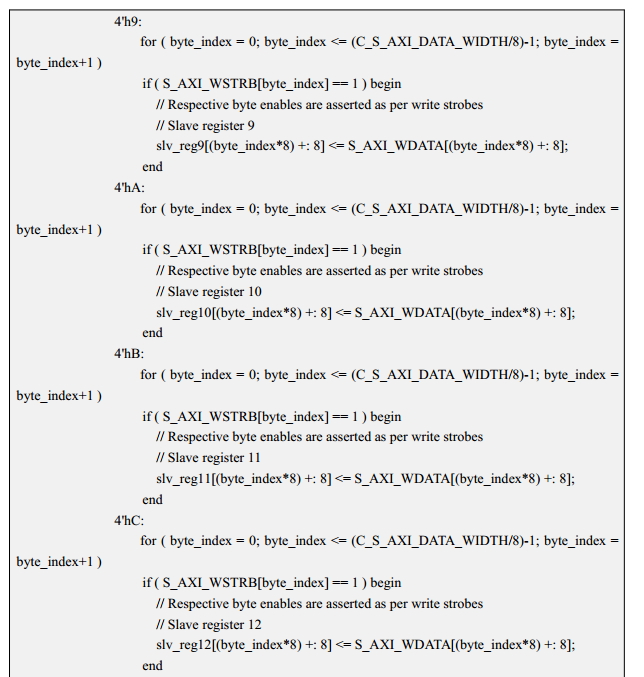

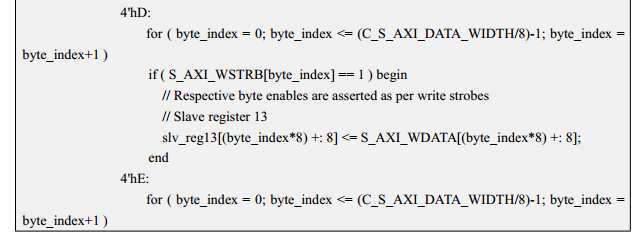

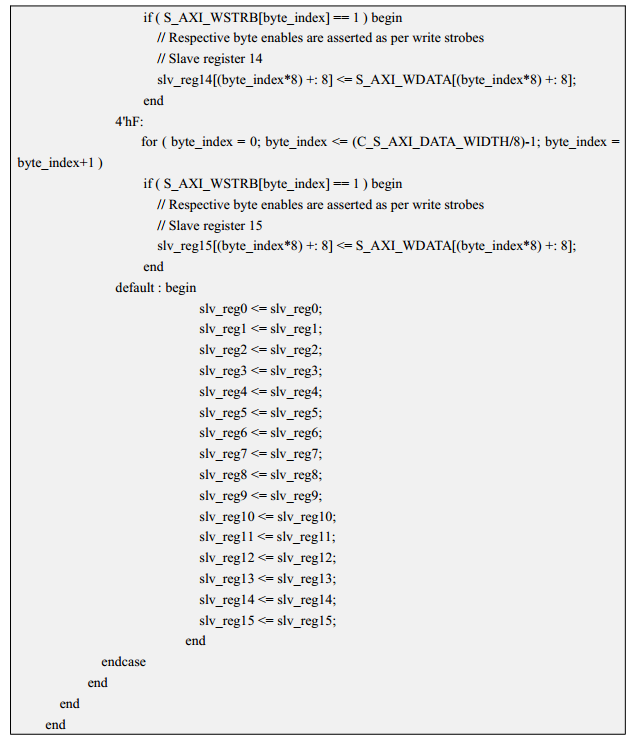

关于AXI写数据的代码

关于PS怎么通过函数读取AXI总线上的数据,后面有例程进行解释。

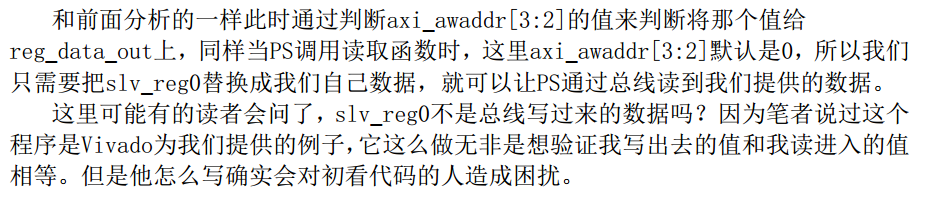

此always块使用的总线时钟,和总线上的复位信号,rlcd_rgb 存储slv_reg0的数据,即:

PS-> slv_reg0(write)-> rlcd_rgb

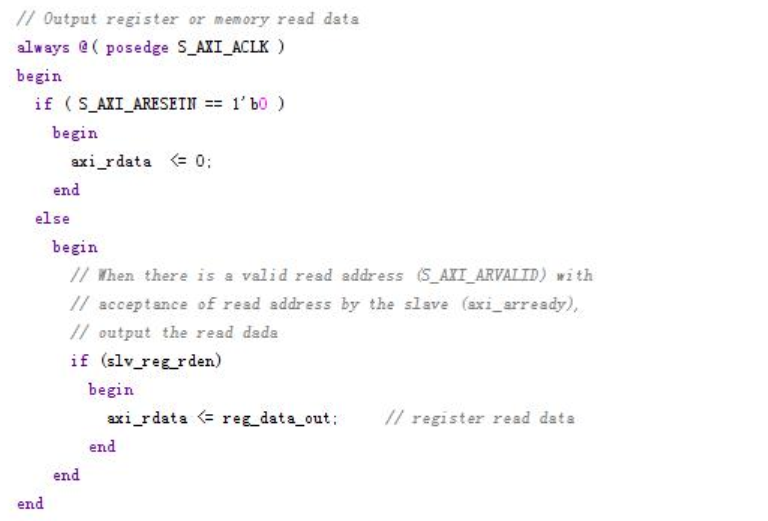

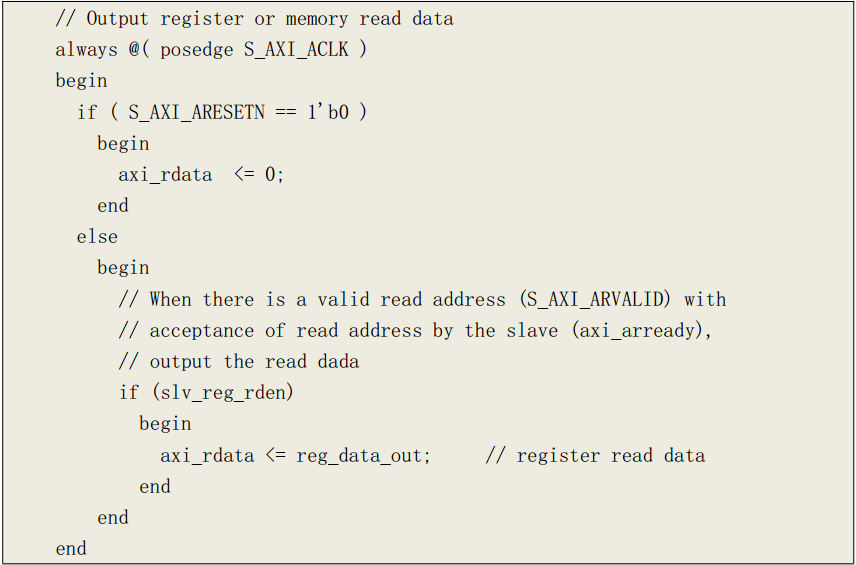

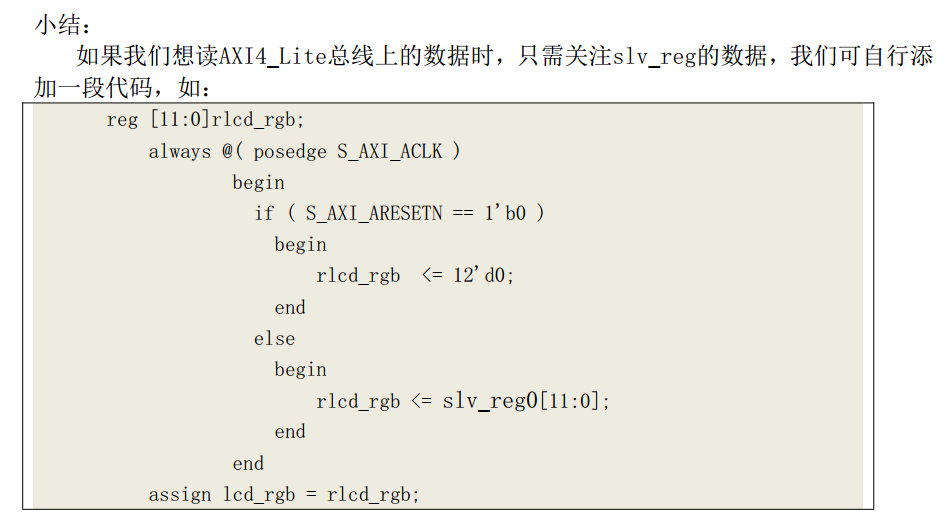

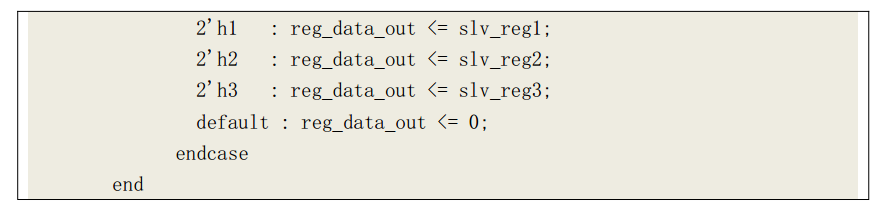

以上操作即是: wlcd_xy -> reg_data_out -> axi_rdata, 将wlcd_xy的数据传递到AXI总线上,让PS进行读取。

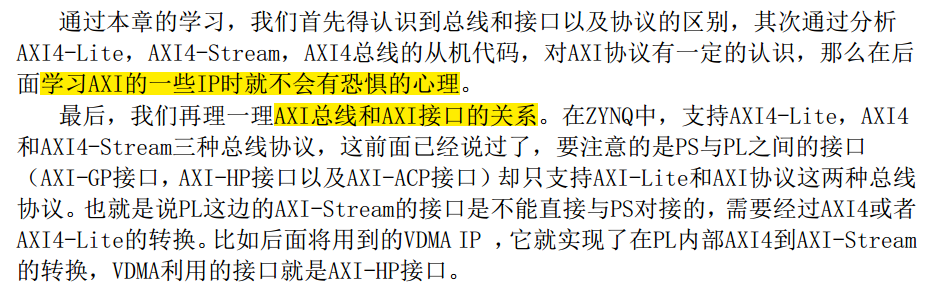

AXI-Stream PS不支持,需要进行转换。

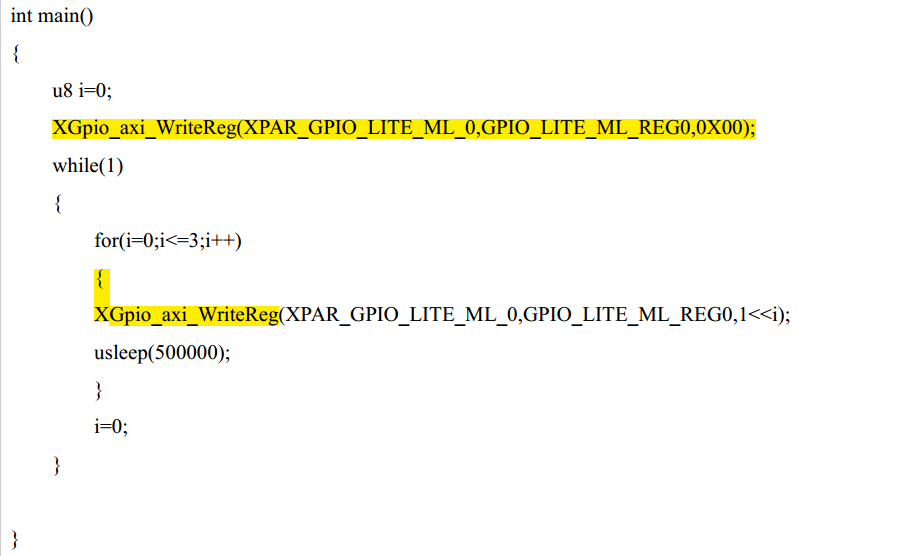

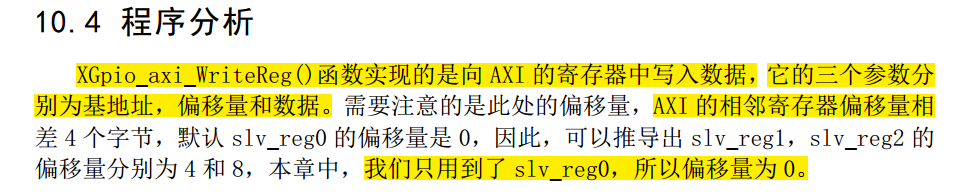

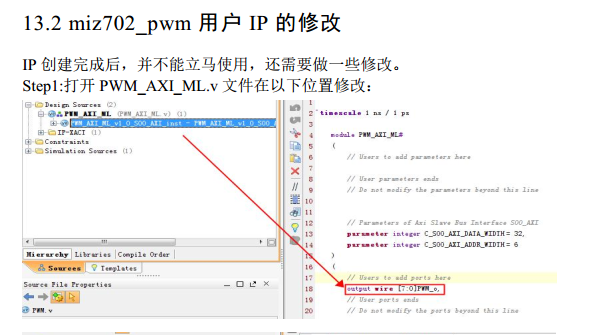

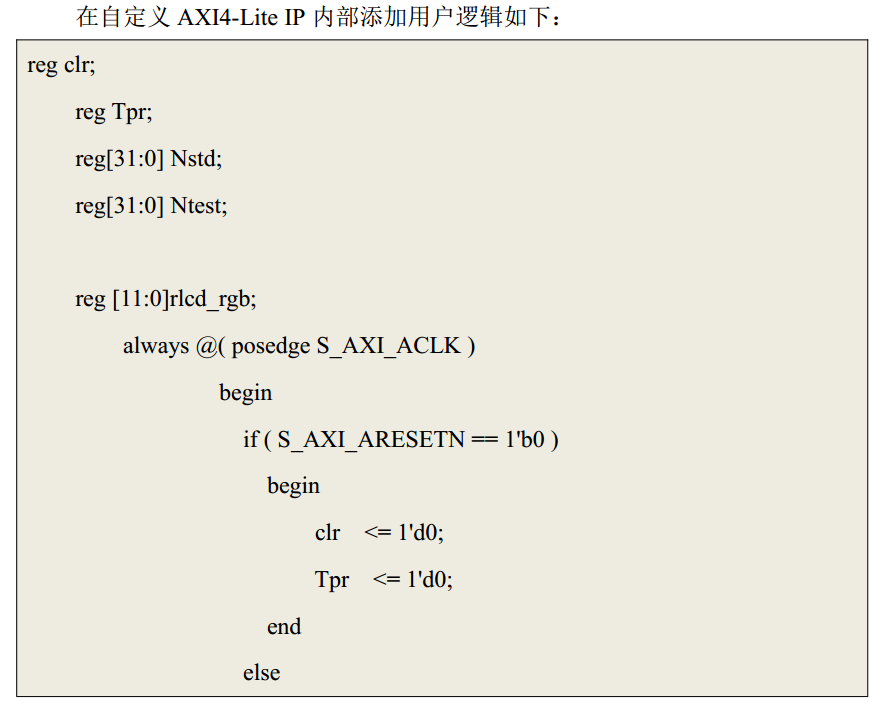

第二个例子

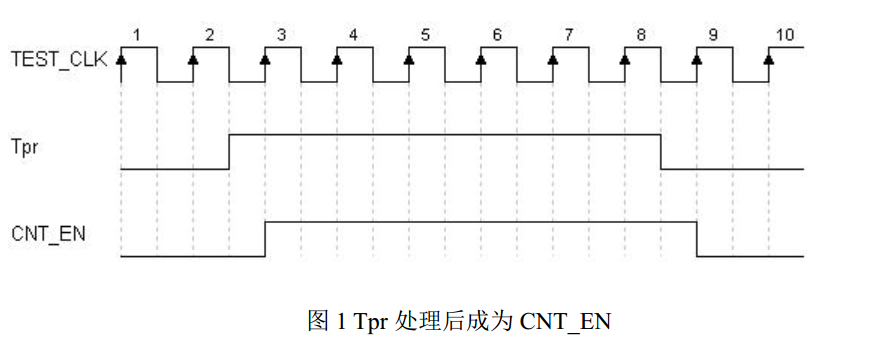

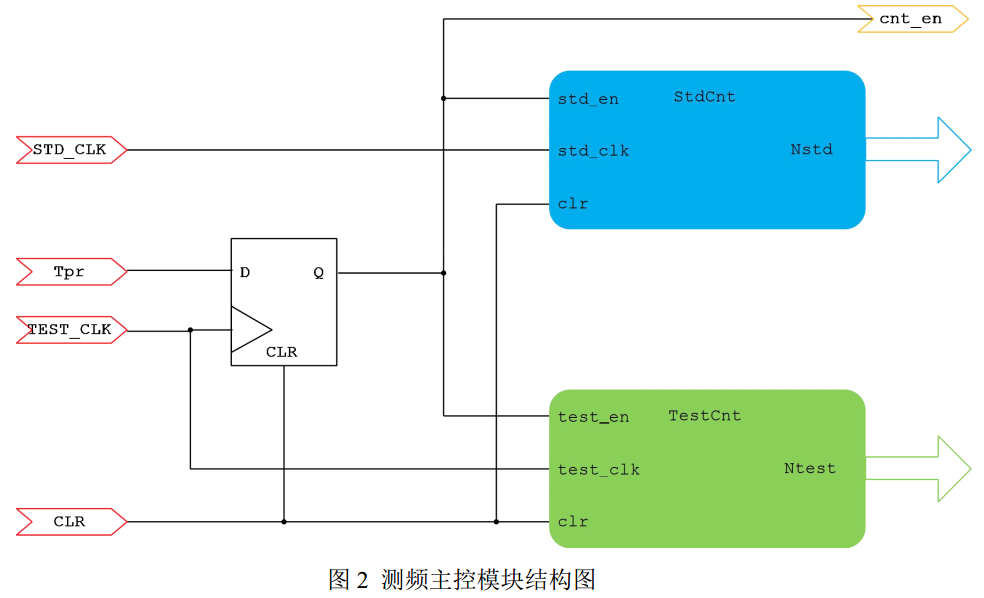

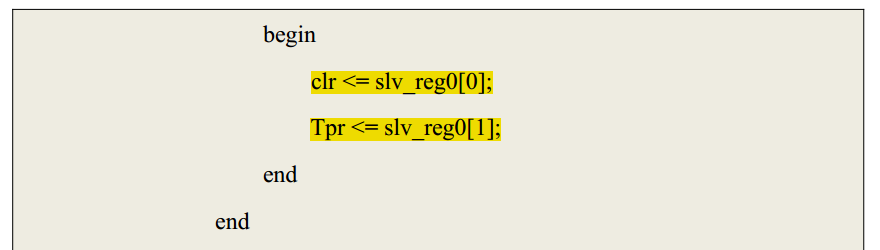

PS写寄存器slv_reg 然后控制clr, Tpr信号。

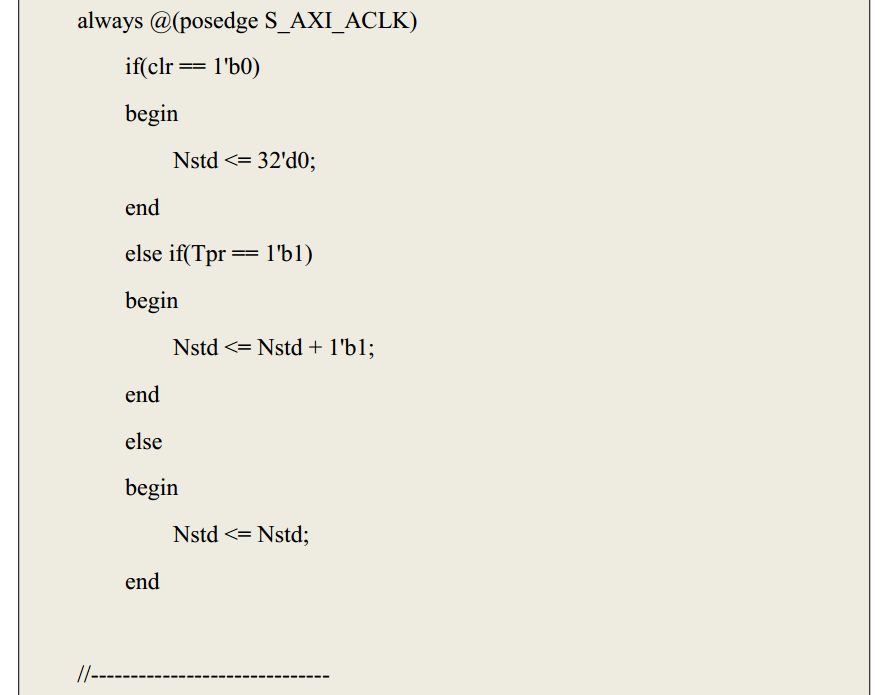

clr, Tpr 用来控制 Nstd的计数,时钟采用的是总线时钟

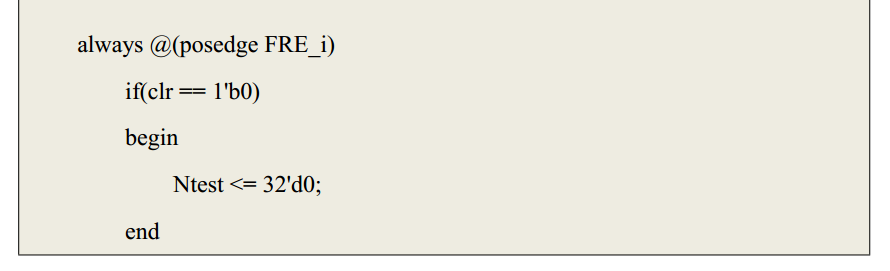

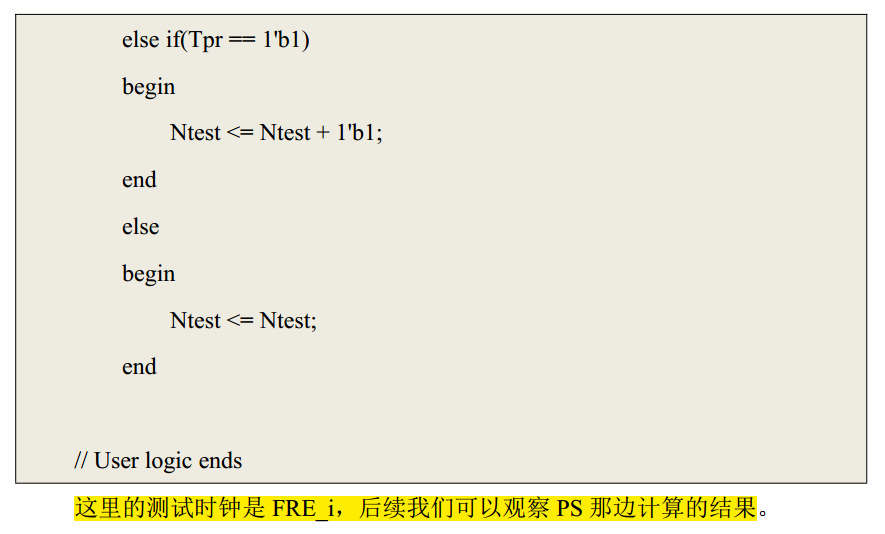

clr, Tpr 控制Ntest计数,采用的是被测时钟FRE_i。