数据与地址的自动给定---基于状态机

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: chensimin // // Create Date: 2018/02/07 14:54:19 // Design Name: // Module Name: top // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module top( input wire clk, input wire rst, output wire [6:0]addr_o, output wire [6:0]data_o ); //------------------------------------------------------

三段式状态机

parameter IDLE = 0, STATE_1 = 1, EDN = 2; reg [6:0]current_state; reg [6:0]next_state; reg [6:0]addr_o_r; reg [6:0]data_o_r; always @(posedge clk or posedge rst) begin if(rst) current_state <= 0; else current_state <= next_state; end always @(*) begin next_state = IDLE; //next_state在更新前,保证其为IDLE状态,和控制信号开始置0是相同的做法,保证了每次状态机都能完整的执行 case(current_state) IDLE: begin next_state = STATE_1; end STATE_1: begin next_state = EDN; end EDN: begin next_state = IDLE; end endcase end //更新输出信号,用自动产生的addr 和 data信息 always @(posedge clk or posedge rst) begin if (rst) begin addr_o_r <= 0; data_o_r <= 0; end else begin case(current_state) IDLE: begin addr_o_r <= addr; data_o_r <= data; end default: begin addr_o_r <= addr; data_o_r <= data; end endcase end end assign addr_o = addr_o_r; assign data_o = data_o_r; //---------------------------------------------------

首先写一个索引信号,在状态机current_state==0时,自动增加

reg [6:0]i; always @(posedge clk or posedge rst) begin if(rst) i <= 0; else if(current_state == 0) if( i<=15 ) i <= i + 1'b1; else i <= 0; end //----------------------------------------------------

在状态机current_state==0时,根据产生的索引信号,来更新地址和数据的值

reg [6:0]addr; reg [6:0]data; always @(posedge clk or posedge rst) begin if (rst) begin addr <= 0; data <= 0; end else if (current_state == 0) begin case(i) 0: begin addr <= 10; data <= 10; end 1: begin addr <= 11; data <= 11; end 2: begin addr <= 12; data <= 12; end 3: begin addr <= 13; data <= 13; end 4: begin addr <= 14; data <= 14; end 5: begin addr <= 15; data <= 15; end 6: begin addr <= 16; data <= 16; end 7: begin addr <= 17; data <= 17; end 8: begin addr <= 18; data <= 18; end 9: begin addr <= 19; data <= 19; end 10: begin addr <= 20; data <= 20; end 11: begin addr <= 21; data <= 21; end 12: begin addr <= 22; data <= 22; end 13: begin addr <= 23; data <= 23; end 14: begin addr <= 24; data <= 24; end 15: begin addr <= 25; data <= 25; end default: begin addr <= 0; data <= 0; end endcase end end endmodule /* add_force {/top/clk} -radix hex {0 0ns} {1 50000ps} -repeat_every 100000ps add_force {/top/rst} -radix hex {1 0ns} {0 200ns} */

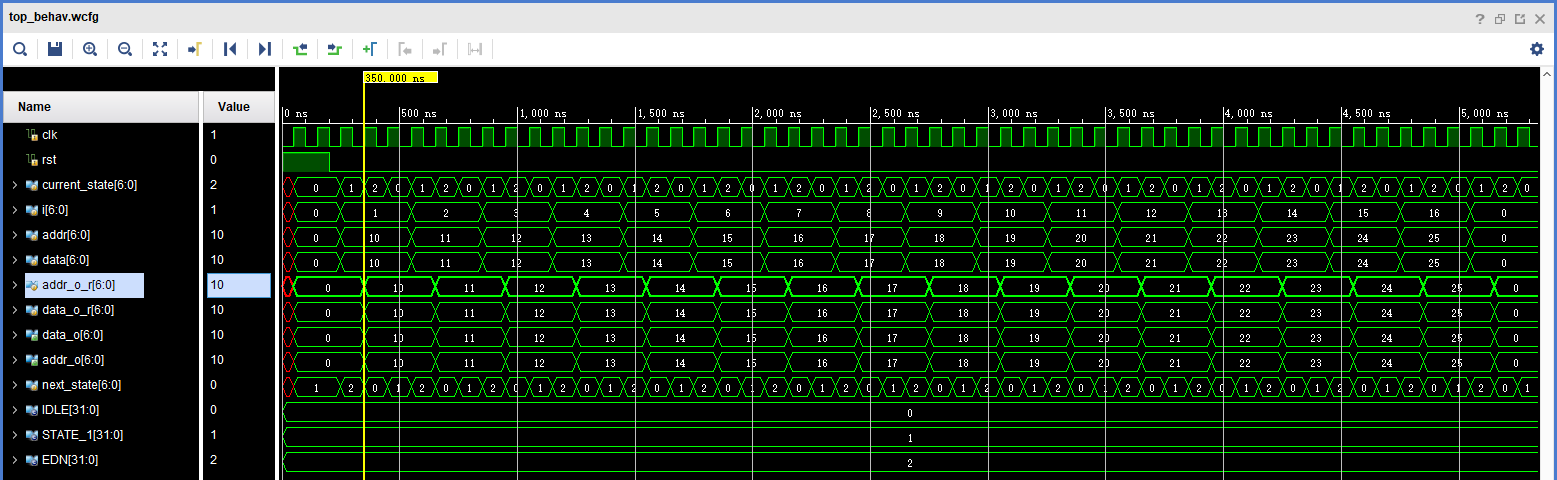

仿真波形: