代码分析

1.DDR时钟的配置

外部输入25M的时钟,经过clocking wizard后,分成三个时钟,200M,5M,25M。

注意:clocking wizard 的reset端口可以直接拉低写0,不用复位。

200M时钟提供给DDR使用。

此处需要弄清楚DDR的某些端口:ui_clk,ui_clk_sync_rst等的使用。

5M的时钟用于系统开机延时模块,目前还不清楚这个开机延时产生的delay_done信号的作用在哪里。

25M时钟提供给了led_map使用。

以后深究。

对于异步信号进入某个模块,先对此模块进行同步处理:

如果信号A是1bit:

Reg [2:0]A_r;

A_r <= {A_r[1:0],A};

最后使用的时候取A_r[2]即可。

如果信号B不是1bit位宽,是8bit宽,则处理办法为延时3个时钟周期,在同一个always块中执行

Reg [7:0]B_r_0;

Reg [7:0]B_r_1;

Reg [7:0]B_r_2;

B_r_0 <= B;

B_r_1 <= B_r_0;

B_r_2 <= B_r_1;

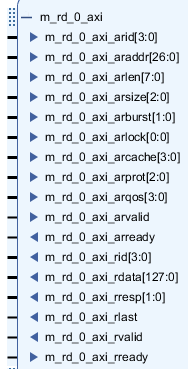

2.AXI_interconnect模块的分析

将axi_interconnect模块导入block_design: