verilog代码 想法验证---与寄存器输出有关

1.

module test_mind( input wire clk, input wire reset, input wire i, output wire A, output wire B ); reg reg_A; always @ (posedge clk or negedge reset) if(reset) reg_A <= 1'b0; else if(i) reg_A <= 1'b1; else reg_A <= 1'b0; reg reg_B; always @ (posedge clk or negedge reset) if(reset) reg_B <= 1'b0; else if(reg_A) reg_B <= 1'b1; else reg_B <= 1'b0; assign A = reg_A; assign B = reg_B; endmodule

2.

add_force {/test_mind/clk} -radix hex {0 0ns} {1 50000ps} -repeat_every 100000ps

add_force {/test_mind/reset} -radix hex {1 0ns} {0 100000ps}

add_force {/test_mind/i} -radix hex {0 0ns} {1 850000ps} {0 950000ps}

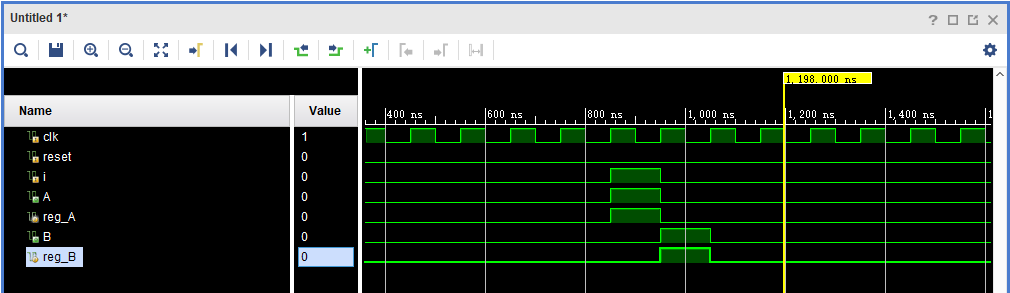

3.

4.

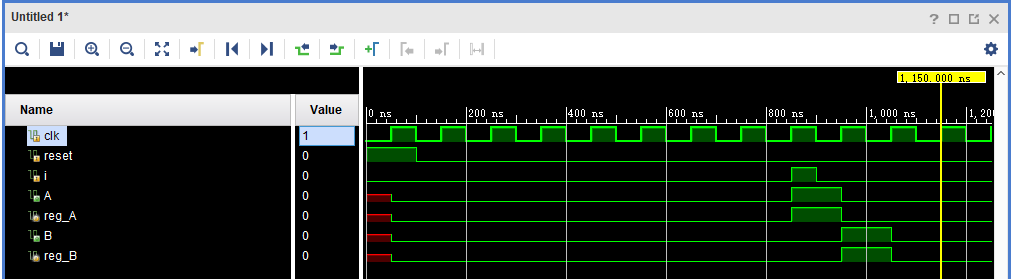

add_force {/test_mind/clk} -radix hex {0 0ns} {1 50000ps} -repeat_every 100000ps

add_force {/test_mind/reset} -radix hex {1 0ns} {0 100000ps}

add_force {/test_mind/i} -radix hex {0 0ns} {1 850000ps} {0 900000ps}

5.

结论:1.第二级寄存器还是会比第一级延时一个周期

2.输入信号一点被采集到,即使在一个时钟周期内发生跳变,也不会影响寄存器的输出结果。