代码分析与仿真

1.

module top( input wire clk, input wire reset, input wire video_cap_buffer_empty ); reg [2 :0] video_cap_buffer_empty_d ; always @ (posedge clk) begin video_cap_buffer_empty_d <= {video_cap_buffer_empty_d[1:0], video_cap_buffer_empty} ; end reg video_cap_buffer_not_empty ; always @ (posedge clk or posedge reset) if (reset) video_cap_buffer_not_empty <= 1'b0 ; else video_cap_buffer_not_empty <= video_cap_buffer_empty_d[2] & ~video_cap_buffer_empty_d[1] ; /*------------------------------------------------------------------------- add_force {/top/clk} -radix hex {0 0ns} {1 50000ps} -repeat_every 100000ps add_force {/top/reset} -radix hex {1 0ns} {0 100000ps} add_force {/top/video_cap_buffer_empty} -radix hex {0 0ns} {1 550000ps} {0 650000ps}

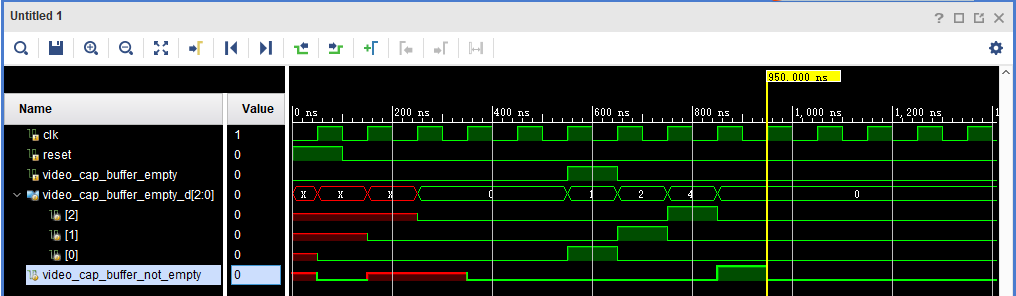

仿真结果为: